Projekt ELEKTRONIČKA META

- Uvod

- Senzori

- Detektorska elektronika (diskretna)

- Detektorska elektronika (CPLD)

- Monitor

- Bežični link

Brza detektorska elektronika (diskretna)

Osnovni zahtjev koji se postavlja pred našu elektroničku metu je mogućnost sigurne, brze i točne detekcije svih kalibara dijabola i slagova za zračne puške (4,5 do 12,7 mm) koji lete brzinama do 330 m/s pa i brže.

Kod dizajniranja svjetlosne zavjese detektirali smo nekoliko problema koje će biti potrebno rješavati i hardverski:

- Problem detekcije malih projektila (kalibar 4,5 mm) koji u krajnjem slučaju lete točno između dvije laserske zrake (na razmaku 4 mm). Takav projektil siječe dvije susjedne laserske zrake samo sa rubnom površinom od 0,25 mm i to u vrlo kratkom vremenu zbog samog oblika dijabole (sječenje je samo rubom glave i rubom suknjice dijabole). Takva djelomična sjena laserske zrake može stvoriti nedovoljan pad napona na senzoru za sigurno prepoznavanje promjene logičkog stanja. Testovi su pokazali da bi na CPLD bolje bilo koristiti CMOS digitalne ulaze umjesto Schmitt triggera jer čisti CMOS ulazi imaju viši naponski prag prepoznavanja logičke nule.

- Kod detekcije praktički svih kalibara, od 4,5 mm na dalje, može se dogoditi da projektil siječe dvije ili više susjednih laserskih zraka. Softver mora izračunati srednju vrijednost pozicije tih zraka kako bi se prikazala središnja točka prolaza projektila.

- Neki projektili, posebno dijabole, zbog svojeg oblika (glava i košuljica) mogu više puta tijekom preleta presjeći jednu lasersku zraku. To će izazvati višestruke detekcije promjena stanja. Hardver mora reagirati samo na prvu promjenu stanja i zaključati ju dok projektil potpuno ne preleti zavjesu.

- Zbog veličine lasera, svjetlosna zavjesa je posložena u dva reda. To znači da će nastati određeno kašnjenje signala iz drugog reda zavjese u odnosu na prvi. Hardver mora pričekati ovo kašnjenje signala (dok projektil potpuno ne preleti oba reda zavjese) i tek onda zaključati stanje.

Ukratko, različiti projektili zbog svojeg kalibra i oblika u većini slučajeva neće presijecati laserske zrake čitavom svojom širinom i duljinom te ih neće svaki puta sječi u potpunosti. To može izazvati višestruke serijske detekcije, višestruke paralelne detekcije i nedefiniranu zonu detekcije (između nule i jedinice). Sve ovo je treba kompenzirati hardverski ili softverski u detektorskoj elektronici.

Kritični slučaj za detekciju: dijabola nepravilnog oblika i malog kalibra prolazi točno između dvije laserske zrake. Podsjetnik na problem koji smo opisali u objavi o dizajnu svjetlosne zavjese.

Kritični slučaj za detekciju: dijabola nepravilnog oblika i malog kalibra prolazi točno između dvije laserske zrake. Podsjetnik na problem koji smo opisali u objavi o dizajnu svjetlosne zavjese.

Rješavanje problema djelomičnog i potpunog presijecanja laserske zrake

Dosadašnjim testovima svjetlosne zavjese našli smo optimalnu kombinaciju struje (jačine) lasera i vrijednosti anodnog otpornika senzora za najbolju detekciju. Sustav je posve imun na bilo kakvo ambijentalno ili dnevno svjetlo.

Međutim, sami laseri nisu savršeni i nemoguće je posve jednako podesiti sve fokuse te na stotinku ili desetinku milimetra poravnati paralelnost svih laserskih zraka. Stoga će se na različitim dijelovima zavjese dobiti i nešto različiti djelomični padovi napona za krajnji slučaj dijabole od 4,5 mm. Ti padovi naponi mogu biti u granicama 0,9 – 1,4 V ako je nivo logičke jedinice podešen na 2,9 V, odnosno padovi napona su 0,8 – 1,1 V ako je nivo logičke jedinice podešen na 2,2 V.

Napon od 1,4 V je granični za CMOS ulaze, a napon od 1,1 V je graničan za Schmitt trigger ulaze. Najbolje bi stoga bilo koristiti 1,1 V za CMOS ulaze. Schmitt trigger ulazi imaju prednost zbog svoje histereze (izbjegavanje graničnog neodređenog stanja) i oblikuju čist digitalni signal za daljnju obradu. Ako isključimo Schmitt triggere, dobivamo veći prag detekcije logičke nule ali i „sirove“ detektorske impulse za daljnju obradu.

Problem bi se mogao riješiti ugradnjom brzog komparatora za svaki senzorski kanal, međutim, to je neisplativa nadogradnja s obzirom na prednosti koje time dobivamo. Komparatori koliko god brzi bili opet unose svoje kašnjenje, a oni su ionako potrebni samo za neke slučajeve preleta dijabola kalibra 4,5 mm. Kalibri 5,5 mm i veći bez problema funkcioniranju na čistoj svjetlosnoj zavjesi (pad napona bolji od 0,9 V).

Mislim da ćemo morati napraviti realne testove sa dijabolama 4,5 mm kad sustav bude završen. Ako se pokažu izostanci nekih detekcija preleta, onda možemo napraviti upravljački krug koji će za kalibre 4,5 mm sniziti napon za prag detekcije logičke jedinice i nule, s obzirom da i dalje postižemo razliku napona od 1,1 – 1,5 V, a histereza Schmitt triggera je tipično 0,6 V do 0,8 V.

Rješavanje problema obrade višestrukih i nejednakih signala iz senzora

Drugi problem koji moramo riješiti su nepravilni izlazni impulsi koje uzrokuju višestruki prekidi i kašnjenja u prekidima zrake. Kada dijabola svojim oblikom siječe lasersku zraku, kako smo prije opisali, ona tijekom preleta može uzrokovati više logičkih promjena stanja (0 -> 1 -> 0 -> 1 -> 0) te svakako međusobno kašnjenje signala sa dvije susjedne laserske linije. Ta frekvencija promjena stanja kao i vrijeme kašnjenja može biti vrlo različito, ovisno o obliku, veličini i brzini dijabole. U nekom najgorem slučaju gdje bi brzina dijabole bila ispod 10 m/s, na 8 mm dužine kašnjenje može biti i do 10 ms.

Naš sustav detekcije dakle mora paralelno pratiti 128 linija (bitova) sa senzora koji mogu dati višestruke binarne nizove signala različitih širina i sa različitim vremenskim razmacima u širokom rasponu između 300 ns i 10 ms. Svaki prelet specifičnog projektila (veličina, oblik, brzina) kroz određeni dio optičke mreže, dati će drugačiji uzorak signala. Uz sve to, obrada signala sa svih 128 senzora mora biti obavljena u vremenu kraćem od 3 µs (najbolje ne dužem od 1 µs).

RS latch (RS zasun)

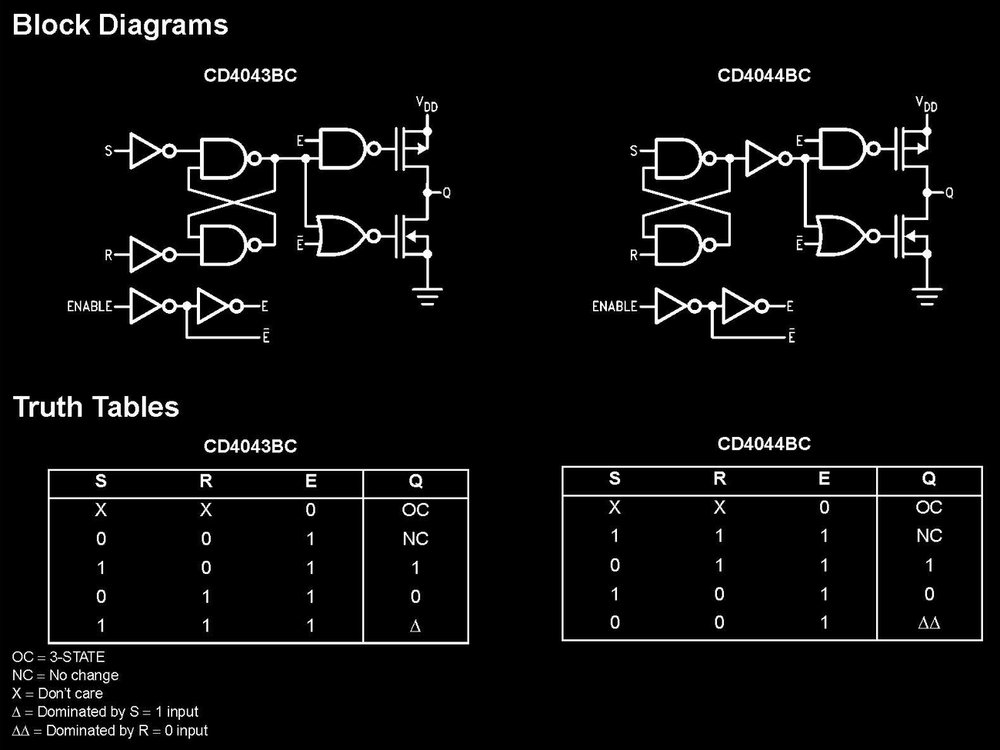

Za rješavanje problema višestrukih signala bio bi idealan logički čip koji sadrži RS-Latch krugove. Iako to nije jedina opcija, svakako je najjednostavnija jer bi upotreba nekih drugih flip-flopova i memorija prilično zakomplicirala hardver i softver projekta. RS-Latch sadrži dva logička ulaza (Set i Reset) te jedan logički izlaz (Q).

Blok sheme jednih (od četiri) RS-Latcheva sadržanih u integriranim krugovima CD4033 i CD4044. Razlika između ova dva čipa je u reakciji na logičke razine na ulazima. Kod CD4043 (NOR Latch) ulazi su aktivni na visokoj razini (Active HIGH), dok su kod CD4044 (NAND Latch) ulazi aktivni na niskoj razini (Active LOW).

Blok sheme jednih (od četiri) RS-Latcheva sadržanih u integriranim krugovima CD4033 i CD4044. Razlika između ova dva čipa je u reakciji na logičke razine na ulazima. Kod CD4043 (NOR Latch) ulazi su aktivni na visokoj razini (Active HIGH), dok su kod CD4044 (NAND Latch) ulazi aktivni na niskoj razini (Active LOW).

Gledano za našu primjenu, RS-Latch CD4044 radi na ovaj način:

- Svaki senzor (foto-dioda) je spojena preko otpornika na pozitivni pol napajanja (+5V) tako da u aktivnom stanju daje na izlazu logičku 0. Schmitt inverteri logičku 0 okreću u logičku 1. Te logičke jedinice sa senzora u mirnom stanju dovode se na pojedinačne SET ulaze RS-Latcheva. RESET pinovi svih RS-Latcheva su spojeni zajedno preko pull-up otpornika (logička 1). Ova RESET linija se spaja na MCU. Time su u mirnom stanju (stanju čekanja) na oba ulaza RS-Latcha (SET i RESET) logičke 1. Izlaz (Q) je pri tome logička 0.

- Kada projektil prekine jednu lasersku zraku, na senzoru će se pojaviti logička 1, a na izlazu iz invertera logička 0. Sada je SET ulaz na 0, a RESET ulaz je na 1. Ovo će uzrokovati promjenu stanja na izlazu iz 0 u 1. To stanje će se trajno zadržati, odnosno ostati će zapamćeno (memorirano) bez obzira kako se kasnije mijenjaju stanja na SET ulazu (ponovna promjena na 0 kada projektil proleti).

- Nakon što MCU pročita novo stanje, resetira sve RS-Latcheve tako da zajednički pin RESET kratkotrajno postavi na 0, a zatim opet vrati na 1.

Potreban nam je dakle jedan RS-Latch za svaki senzor. RS-Latch mijenja i zaključava izlazno stanje čim dijabola prvi put prekine jednu od laserskih zraka, pri čemu je posve nebitno da li će prekid biti kraći, duži, višestruki, sa većim ili manjim razmacima. MCU (Arduino) nakon toga ima sve vrijeme svijeta (i 500 ms ako treba) očitati svih 128 stanja na izlazima RS-Latcheva, nakon čega može promijeniti stanje na Reset pinu i sve Latcheve ponovno resetirati na 0 za novi ciklus detekcije.

Jedini brzi čipovi koji nam ovdje trebaju su dakle Schmitt inverteri SN74HC14 (30 ns) i RS-Latchevi koji po četiri komada dolaze u integriranom krugu CD4044. Vrijeme odziva (promjene stanja) ovih čipova je 20-350 ns, ovisno o naponu napajanja (3-15 V) i pinovima na kojima se promjena događa. To je dovoljno brzo za naše potrebe, no šteta što se više ne može nabaviti 74HC4044 inačica ovog čipa (High-speed CMOS) koja je deset puta brži od standardne CD CMOS serije.

3-state stanje izlaza

CD4044 je inače „3-state“ logički integrirani krug što znači da može imati tri izlazna stanja: logička 0, logička 1 i tzv. stanje visoke impedancije (High Z ili Hi-Z). U Hi-Z stanju izlazi iz logičkog čipa zauzimaju stanje visoke impedancije (velikog unutrašnjeg otpora) te se spojeni u strujni krug ponašaju praktično kao beskonačni otpor i električki ne utječu na krug (kao da nisu spojeni). Ovo je korisno ako se izlazi više logičkih krugova spajaju zajedno. Tada se preko pina Enable može uključiti samo onaj čip, odnosno samo onaj logički izlaz koji nam je u tom trenutku potreban. Za našu primjenu ova funkcija nije iskoristiva tako da će pin Enable uvijek biti uključen (na logičkoj 1).

Zabranjeno stanje ulaza

Na blok dijagramu i tablici istine također vidimo da postoje kritična (nestabilna, zabranjena, nepredvidljiva) logička stanja ulaza. Za CD4043 nastaje takvo stanje kada su oba ulaza na logičkoj 1, a kod CD4044 kada su oba ulaza na logičkoj 0. Ova stanja krše osnovnu logiku RS-Latcha.

Uzmimo za primjer CD4044 koji ćemo mi koristiti za projekt (kod CD4033 je pojava ista samo obrnuta glede logičkih stanja). Ako su oba ulaza 0 (S=0, R=0) izlaz (Q) ide u logičku 1 jer kod NAND RS-Latcha nula na bilo kojem ulazu “prisiljava” izlaz na 1. U ovom stanju čip ne “pamti” ništa, on samo slijedi ulaze. Problem nastaje u trenutku kada oba ulaza istovremeno pokušavamo vratiti u početno mirno stanje, odnosno na logičke 1. Na shemi u tablici istine vidimo da za oba ulaza 1 izlaz treba ostati 1 (No change). Međutim, da li će izlaz ostati 1 ili pasti na 0, u ovom konkretnom slučaju ovisi isključivo o mikroskopskim razlikama u brzini tranzistora unutar tog konkretnog primjerka čipa ili o tome koji je ulaz (makar i za nanosekundu) prvi dobio napon. To je prilično nepredvidljivo stanje i treba ga izbjegavati.

U konkretno našem slučaju, sustav ušao u ovo nestabilno stanje ako bi se poklopio trenutak kada projektil prekine lasersku zraku sa trenutkom kada Arduino resetira RS-Latcheve. U tom trenutku bi oba ulaza bila 0, što daje izlaz 1, međutim nakon Reseta pri povratku u normalan (mirni) rad (oba ulaza logička 1) došlo bi do te nepredvidive situacije gdje na izlazu može biti 0 ili 1. Tada bi se zabilježen pogodak mogao “izbrisati” sam od sebe ili bi moglo ostati “zakočena” u jedinici.

Mi ćemo ovo stanje svakako izbjeći samim time što će Reset biti moguć i izvršen samo u vremenu kada ne može biti prolaska projektila kroz zavjesu. To je vrijeme od 10 ms nakon detekcije prvog prekida zrake. Tih 10 ms je dovoljno da i najsporiji projektil odavno pređe zavjesu, a svakako da je iz zračne puške nemoguće ispaliti dva hica u tom kratkom vremenskom razmaku. Čak ni tipično automatsko vatreno oružje ne ispaljuje hice tolikom brzinom. Primjerice, čuveni AK-47 ispaljuje 600 metaka u minuti što znači da je vremenska razlika između dva metka 100 ms. Ova meta bi stoga bez problema mogla detektirati i takvu rafalnu paljbu čak i pri brzini zrna od tipičnih 720 m/s.

Multipleksiranje 128 bita podataka

Nakon što smo RS-Latch memorijama osigurali trajno pamćenje brzih senzorskih impulsa, brzina nam više nije prioritet za daljnju obradu podataka. Razmak između dva hica iz puške je barem 1 sekundu i nama za kompletnu obradu i prikaz pogotka definitivno ne treba brzina veća od brzine treptaja oka (100-400 ms) iako će vrijeme obrade sigurno biti i puno kraće od toga. Sada nam je umjesto brzine puno važnije multipleksiranje, odnosno kako svesti 128 podatkovnih linija na što je moguće manje poveznih žica prema mikrokontroleru (Arduinu).

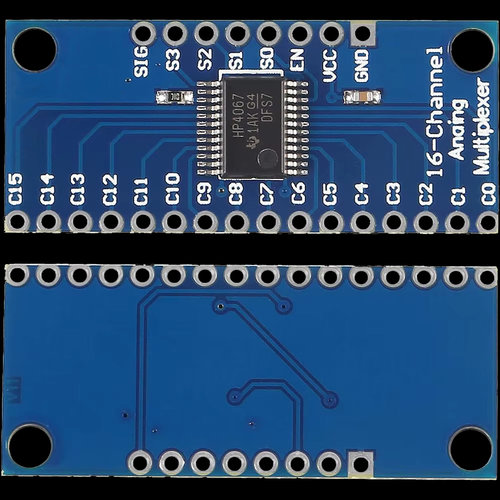

Naravno da sam i ovdje pretražio tržište svih popularnih i jeftinih multipleksora, te je pobjedu na kraju odnio 16-kanalni analogni multipleksor i demultipleksor sadržan u čipu 74HC4067, a koji se vrlo prikladno može kupiti u obliku modula za cijenu od 0,6 eura po komadu. Ovaj čip ne samo što je najjeftiniji nego je i najprikladniji za naš projekt. Opcije koje uključuju komunikacijske protokole ili posmične registre (74HC165) samo bi zakomplicirale stvari.

Analogno ili digitalno multipleksiranje

Kad bi 74HC4067 koristili kao analogni multipleksor praktično bi nam bio dosta jedan jedini ovakav čip. Međutim, analogno multipleksiranje na jeftinim čipovima (10-bit) može dovesti do pogrešaka i svakako traži daleko više vremena za procesuiranja signala.

Za analogno multipleksiranje bi grupe od 8 izlaznih kanala sa senzora morali povezivati preko djelitelja napona sa otpornicima, tako da na svakom od 16 ulaznih kanala multipleksora imamo 8 različitih (analognih) nivoa napona sa pojedinih linija senzora. Tu bi svakako trebali paziti na raspored povezivanja kako bi se ispravno detektirale susjedne laserske linije jer multipleksor ne može razlikovati više od jednog analognog podatka na jednoj ulaznoj liniji. To znači da grupe od 8 senzora ne mogu činiti susjedni senzori, nego svaki 16 senzor dolazi na isti ulaz multipleksora. Sve ovo komplicira hardver i kasnije programiranje, uvelike povećava vrijeme procesuiranja signala, a u konačnici nema ni neke cjenovne uštede u dijelovima. Bolje je koristiti multipleksor 74HC4067 kao čisti digitalni 16-bitni ulaz.

74HC4067 možemo zamisliti kao rotacijsku sklopku s 16 položaja kojom upravlja digitalni signal. On omogućuje da se jedan zajednički pin (SIG – Signal) poveže s bilo kojim od 16 neovisnih kanala (C0 do C15) koji se odabiru preko 4 adresna pina (S0, S1, S2, S3). Nama će trebati 8 ovakvih čipova (svaki čita 16 senzora), a čipovi se pojedinačno redom aktiviraju pomoću pina EN (Enable). Kada je ovaj pin na LOW, čip radi. Kada ga stavite na HIGH, svi kanali su odspojeni (Hi-Z stanje). Ovdje nam je Hi-Z stanje itekako upotrebljivo jer izlaze svih 8 čipova (SIG) možemo spojiti zajedno na jedan I/O port Arduina. Adresne linije se također spajaju paralelno pa do Arduina ide svega 5 zajedničkih linija i 8 Enable linija od svakog čipa.

Konačni odabir elektroničkih komponenti (za sada)

- 22 x SN74HC14: Schmitt inverter (rješava problem različitih nivoa signala sa foto-dioda) – oko 3,5 eura

- 32 x CD4044: Memorija događaja (rješava titranje laserske zrake uslijed prolaza dijabole i kašnjenje signala između dviju laserskih ravnina) – oko 15 eura

- 8 x CD74HC4067: 16-bitni multipleksori (rješavaju problem čitanja velikog broja linija, 128 linija reducira se na njih 13 do Arduina) – oko 5 eura

- Bilo koji jeftini Arduino (glavni kontroler koji samo upravlja adresiranjem i očitavanjem) – oko 3 eura

Praktična izvedba

S obzirom da je ovdje riječ o razvojnom projektu (prototipu), sustav želim podijeliti na više jednakih zamjenjivih modula koje mogu lako nadograđivati, modificirati ili servisirati. U ovoj fazi svakako izbjegavam upotrebu SMD komponenti jer želim imati lak servisni i mjerni dostup svakoj razini elektronike. Kod mene svi čipovi idu u podnožja tako da ih mogu lako testirati i mijenjati u slučaju otkaza i to je najbolji „JTAG“ koji mogu izvesti za ovaj diskretni elektronički projekt

Projektiranje brze detektorske elektronike

Prva zamisao je bila na jedan modul smjestiti 12 senzorskih kanala, što uključuje 2 x SN74HC14 i 3 x CD4044. Problem je što bi to narušilo modularnost multipleksora CD74HC4067 koji ima 16 kanala (trebalo bi više poveznih pinova između modula). Stoga sam se radije odlučio na module koji prihvaćaju 16 senzorskih kanala, dakle 3 x SN74HC14, 4 x CD4044 i 1 x CD74HC4067. Ovdje dva invertera ostaju viška, no to je toliko jeftin čip da se time ne treba zamarati. U konačnici će nam umjesto 22 trebati 24 komada ovih čipova.

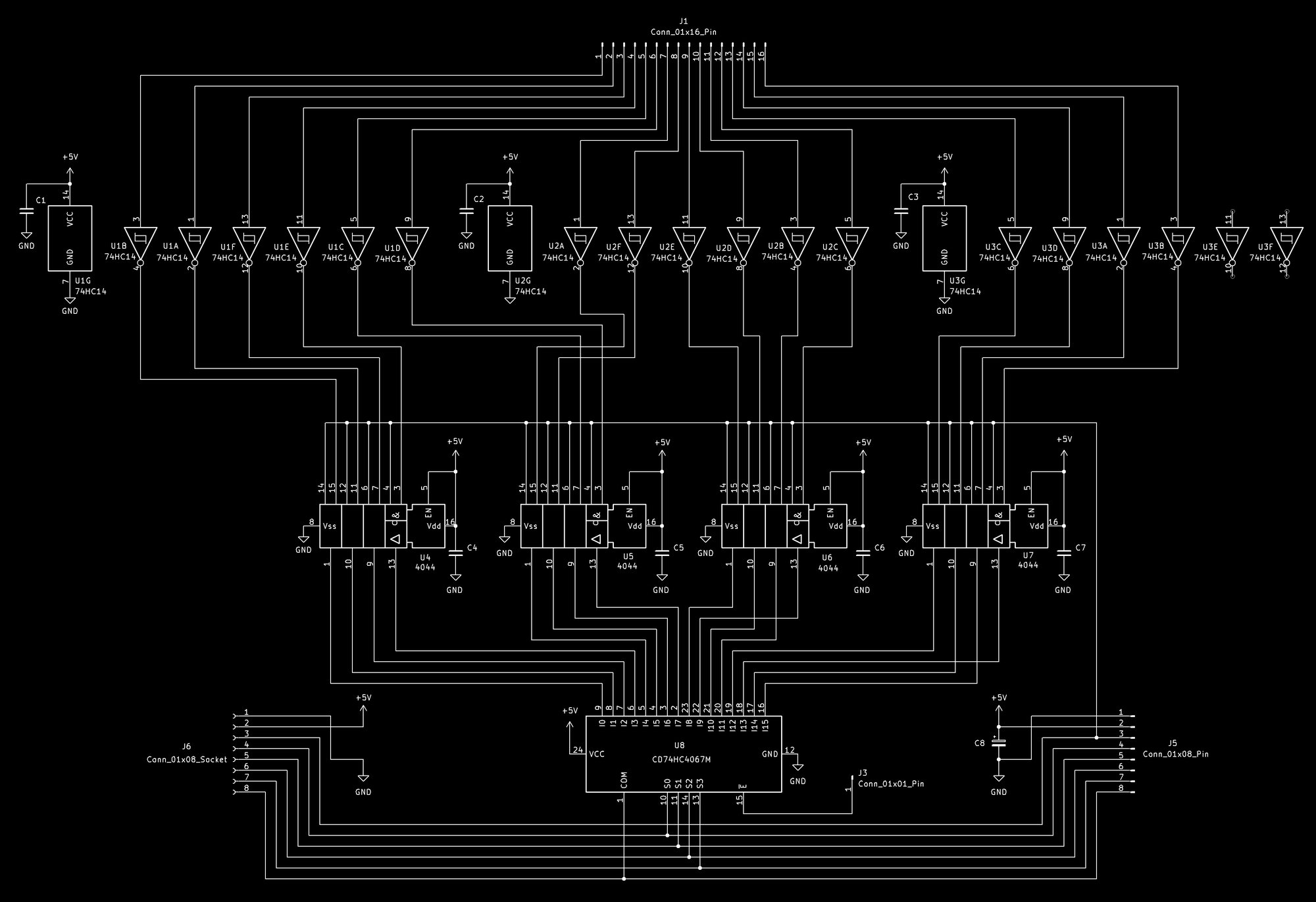

Elektronička shema jednog modula sa 16 kanala nacrtana u KiCad programu. Za čitavu mrežu senzora (2×64 komada) potrebno je 8 ovakvih modula.

Elektronička shema jednog modula sa 16 kanala nacrtana u KiCad programu. Za čitavu mrežu senzora (2×64 komada) potrebno je 8 ovakvih modula.

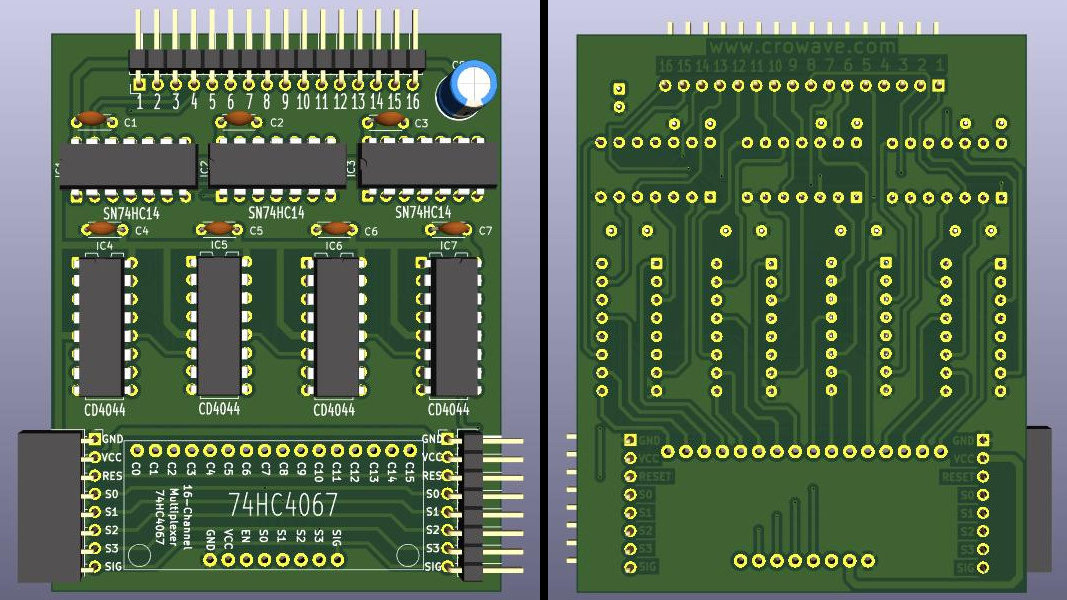

Iako pločica modula sadrži praktično samo logičke čipove, zbog rasporeda njihovih pinova međusobno povezivanje je prilično isprepleteno. Vrlo teško je sve ovo povezati već na eksperimentalnoj ploči, a još teže bi bilo sve ovo zalemiti na nekoj univerzalnoj tiskanoj pločici. Stoga sam u KiCad programu nacrtao dvostranu tiskanu pločicu najmanjih mogućih (razumnih) dimenzija, tako da širina 4 modula ne prelazi 256 mm, kolika je i širina/visina same senzorske mreže.

16-kanalni moduli su širine 63 mm (tolerancija 2 mm) tako da širina modula ne prelazi širinu niza od 16 senzora.

16-kanalni moduli su širine 63 mm (tolerancija 2 mm) tako da širina modula ne prelazi širinu niza od 16 senzora.

KiCad

Ovdje mi nije namjera reklamirati, prezentirati ili preporučiti bilo koji od desetak popularnih programa za crtanje elektroničkih shema i kreiranje tiskanih pločica (PCB). KiCad koristim jer je besplatan i potpuno zadovoljava moje potrebe. Kroz karijeru sam koristio različite programe za istu namjenu. Iako svi rade vrlo slično, ipak je potrebno vrijeme da se upoznate sa menijima, opcijama i specifičnostima pojedinih programa. Tko dobro nauči rad i navikne se raditi u jednom programu, izbjegava prelaziti na neki drugi gdje je opet treba novo učenje i navikavanje.

Ipak, kroz vrijeme neki popularni programi postaju zastarjeli (nema novih nadogradnji i podrške), neki više nisu besplatni ili se jednostavno pojave bolji besplatni programi. Tako sam i ja nakon nekoliko programa trenutno na KiCadu.

Netko tko nije radio sa ovakvim programima može imati predodžbu da će isti jednim klikom miša iz elektroničke sheme nacrtati gotovu tiskanu pločicu, odnosno rutirati tiskane veze. Neki programi to čak i mogu (uz prethodni ručni razmještaj komponenti), međutim, to u praksi vrlo rijetko ispadne dovoljno dobro i optimalno, posebice ako shema spajanja zahtjeva puno tiskanih veza. Tako se i uz KiCad može koristi dodatni program ili integrirati dodatak za automatsko rutiranje (Freerouting plugin ili Replicate Layout plugin), no to može napraviti više zbrke neko koristi.

Zato u KiCadu uvijek koristim samo „polu-automatsko“ rutiranje gdje mi program pomaže da držim zadani razmak između veza i da mi općenito ne dozvoli povlačenje linija izvan zadanih postavki. Kod crtanja pojedinačne veze, program može sam predložiti put kojim veza može proći, no u praksi taj posao (logiku) najbolje obavlja ipak sam čovjek. Program je dobar u dijagnostici da li su sve veze ispravno provučene i odlično radi poslove poput popunjavanja zona za GND.

Ja sam za ovaj projekt čak morao ići obrnutim smjerom. Tiskanu pločicu nisam crtao iz elektroničke sheme, nego izravno. Razlog za to je što je pojedinačni čipovi sadrže puno istih nezavisnih logičkih sklopova (inverteri, SR-Latch) koji se mogu upotrijebiti za bilo koji kanal. Tako kod izravnog crtanja sheme mogu odabrati onaj sklop (pinove) koji najbolje odgovaraju fizičkom povezivanju, odnosno one koji su na najmanjem međusobnom razmaku i koji traže najmanje križanja i zaobilaženja kod povezivanja.

Velika pomoć kod rutiranja veza je iznimno dobar vizualni pogled na pločicu tijekom svih faza izrade, jednako što se tiče 2D prikaza po slojevima kao i 3D prikaza sa svih strana i kutova. Ako se netko još uvijek tvrdo drži „stare škole“ crtanja pločice po papirima, sad je stvarno krajnje vrijeme da pređe na elektroničke programe za PCB. Ti programi su tako dobro i jednostavno napravljeni da se mogu savladati za jedno poslijepodne, a najvažnije je što podržavaju izvoz podataka u različitim formatima za profesionalnu izradu tiskanih pločica, koja je u zadnje vrijeme postala vrlo jeftina.

Praktični problemi oko diskretne logike

Kako sam ja „stara škola“ ovdje je ideja bila koristiti (danas već uglavnom zastarjele) diskretne logičke integrirane krugove za hardverske detektorske krugove. No, upravo tu se krije i praktični problem. Naime, zahvaljujući sve većem razvoju programabilnih FPGA i CPLD čipova te brzih mikrokontrolera, proizvodnja klasičnih logičnih čipova se značajno smanjila. Danas se već vrlo teško pronalaze neki jednostavni logički čipovi koji su bili vrlo rašireni prije 20 ili 30 godina.

Iako smo uspjeli „nagurati“ sve te čipove na mali raspoloživi prostor i logika bi mogla funkcionirati, možda je ipak dobro razmisliti i o nekim modernijim rješenjima. Stoga prelazimo na novo poglavlje razvoja našeg projekta koje smo nazvali CPLD.

Ovo je finalna elektronička shema i tiskana pločica za diskretnu izvedbu senzorske elektronike za 16 kanala. Konektore za spajanje senzora pomaknuo sam bliže sredini kako bi se bolje iskoristio prostor unutar okvira mete. Potrebno bi bilo 8 takvih modula (4 za svaku os).

Iako projekt u diskretnoj elektronici nije neizvediv, puno jednostavnije je ovu elektroniku izvesti pomoću CPLD-a. S obzirom da CPLD radi na 3,3 V sistemu, onda ćemo umjesto ATmega koristiti ESP32 mikrokontrolersku razvojnu pločicu.