AM/FM predajnik za testiranje starih radio prijemnika (sadržaj):

- Uvod i VFO

- AM modulator

- FM modulator

- Audio limiter

- Antena

- Dizajn uređaja

- Testovi

FM modulacija

Frekvencijsku modulaciju oscilatora sa čipom Si5351A možemo izvesti jedino modulacijom njegovog internog oscilatora takta koji je kontroliran vanjskim kristalom od 25 MHz. Potrebno je dakle u ritmu modulacijskog napona (audio signal) mijenjati frekvenciju oscilatora od 25 MHz. Što je modulacijska frekvencija viša i amplitudno jača to će devijacija noseće frekvencije biti veća, a zauzeće frekvencijskog kanala šire. Za kvalitetan prijenos muzike (WFM) ta promjena frekvencije doseže i do ±75 kHz. Kod raznih službenih i radioamaterskih FM veza gdje se prenosi samo govor (NFM) ukupna širina kanala ne smije prelaziti 12 ili 15 kHz. To se postiže ograničavanjem audio frekvencijskog opsega (300 – 3000 Hz) ali i ograničavanjem same devijacije.

Koliko sam uspio istražiti, gotovi moduli kvalitetnijih VCO-a za 25 MHz prilično su skupi i neisplativo je kupovati više takvih modula za naš projekt.

Nama je za na naš modul Si5351A potreban što stabilniji oscilator takta jer o njemu ovise sve druge generirane noseće frekvencije. Logično bi stoga bilo zadržati kristalni oscilator, odnosno izvesti FM modulaciju kristalnog oscilatora. Međutim, izravna FM modulacija kristalnog oscilatora je vrlo teška upravo iz razloga jer je kristal vrlo stabilan na svojoj rezonantnoj frekvenciji. To znači da je moguće izazvati tek vrlo male promjene osnovne frekvencije koje neće dati dovoljnu devijaciju za kvalitetnu FM modulaciju. Inače, kod komercijalnih kristalnih FM predajnika, ta mala frekvencijska devijacija osnovnog oscilatora, duplira se kasnijim stupnjevima umnoživača frekvencije. Svakim umnožavanjem osnovne noseće frekvencije (izdvajanje drugog ili trećeg harmonika) umnožava se i početna devijacija. Potrebno je 3-5 stupnjeva umnožavanja da se postigne dovoljna FM devijacija.

Drugi način je iskoristiti harmoničke frekvencije overtonskih kristalnih oscilatora. Mi bismo ovdje umjesto kristala na 25 MHz mogli ugraditi kristalni oscilator na 5 MHz. Taj oscilator bi se frekvencijski modulirao, te zatim izdvojio peti harmonik, na kojem je pet puta umnožena osnovna frekvencija, a jednako tako i devijacija osnovne frekvencije. Trebali bi dakle izgraditi pojasni filtar za 5. harmonik (25 MHz), te dodati pojačalo za izlazni signal jer će 5. harmonik sasvim sigurno biti preniske razine za takt frekvenciju čipa Si5351A. Ovo je svakako nešto jednostavniji sklop od prethodnog prijedloga, no trebalo bi vidjeti u praksi da li bi to stvarno funkcioniralo.

Treća mogućnost je odustajanje od kristalnog oscilatora i gradnja nekog jednostavnog oscilatora na 25 MHz kojeg je lako frekvencijski modulirati. Frekvencija takvog oscilatora vjerojatno neće biti stabilna kao kod kristalnog oscilatora ali za testni predajnik će i ta stabilnost biti više nego dovoljna.

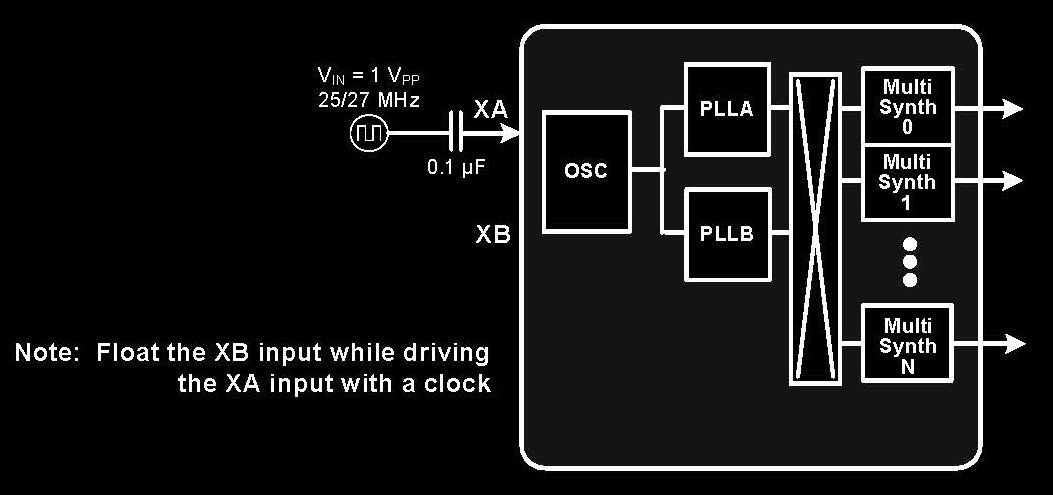

Prvi test FM modulacije

Prije gradnje FM modulatora moramo isprobati da li će čip Si5351A uopće raditi sa FM moduliranim takt signalom. Sretna okolnost je ta da se kao oscilator takta za Si5351A ne mora nužno koristiti interni oscilator sa vanjskim kristalom u opsegu frekvencija 25-27 MHz, nego se može koristiti i bilo koji drugi vanjski signal frekvencije 10-100 MHz (max. 3,6 Vpp). Inačica čipa Si5351B ima poseban pin VC (VCXO) na naponsku kontrolu oscilatora, a inačica Si5351C ima pin CLKIN za dovođenje vanjske frekvencije takta, te bi se ovi pinovi možda mogli iskoristiti za FM. Kod naše osnovne inačice Si5351A pak vanjski takt od 25-27 MHz možemo dovesti na pin XA preko kondenzatora 100 nF (nakon što se ukloni vanjski kristal), a ulaz XB pri tome ostaje otvoren (neiskorišten).

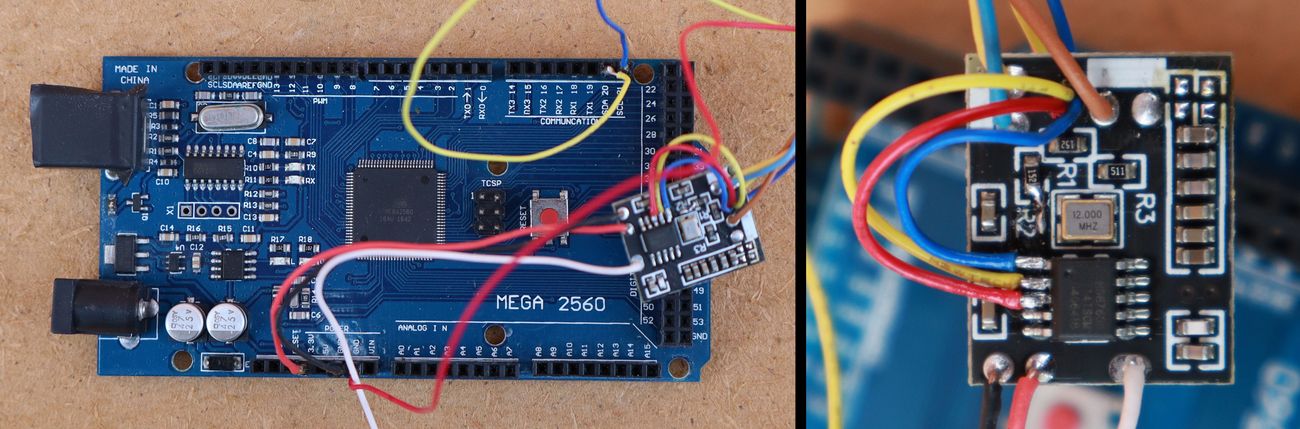

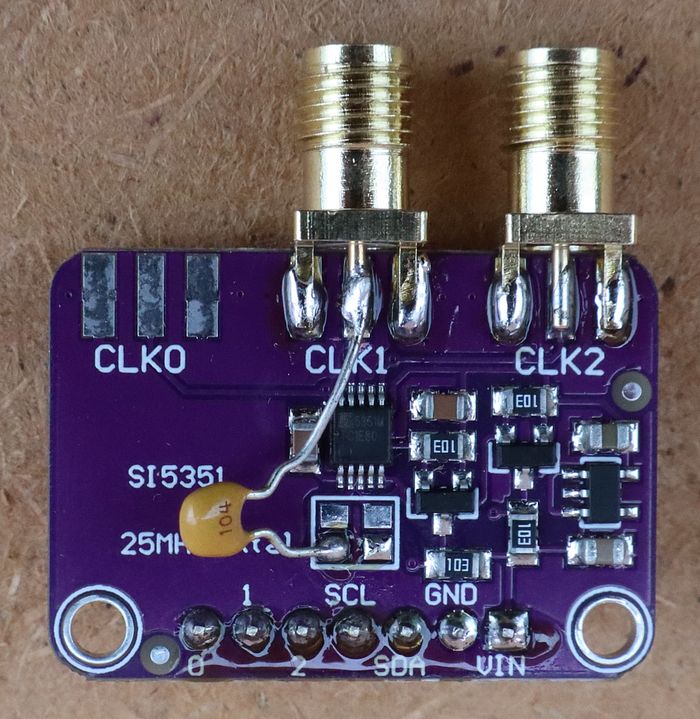

Modul Si5351 sa odlemljenim kristalom 25 MHz i pripremom za dovođenje takt signala 25 MHz iz nekog vanjskog oscilatora. Konektor u sredini je odspojen od pločice (prerezana tiskana veza) i iskorišten za dovod takt signala.

Modul Si5351 sa odlemljenim kristalom 25 MHz i pripremom za dovođenje takt signala 25 MHz iz nekog vanjskog oscilatora. Konektor u sredini je odspojen od pločice (prerezana tiskana veza) i iskorišten za dovod takt signala.

Prvi testovi su pokazali da FM sasvim dobro radi na frekvenciji takt signala. Primijetili smo da je FM signal puno čišći kada se koristi (modulira) sinusni takt signal (bez harmonika) nego kad se koristi pravokutni signal. To je i za očekivati jer se modulacijom pravokutnog signala istovremeno modulira i niz harmonika koji onda stvaraju čitav spektar novih harmoničkih frekvencija. Neke od tih frekvencija padaju u FM prijemni opseg gdje se miješaju sa frekvencijama originalnog modulacijskog signala te ga izobličavaju.

Zbog svega ovoga postoji dvojba da li je bolje ići na FM modulator baziran na pravokutnom signalu (koji je jednostavniji za gradnju) ili pak ići na sinusni signal, odnosno na oscilator sa podešenim rezonantnim LC krugom. Najjednostavniji FM oscilator (VCO) može se napraviti uz upotrebu NAND logičkih vrata.

Lijevo na slici je osnovna shema oscilatora sa NAND vratima, a desno je shema testnog FM modulatora 25 MHz za naše potrebe.

Logički ili digitalni integrirani krugovi, odnosno logička vrata su kao što znamo predviđena za rad sa dvije naponske razine: niski napon blizu ili na razini nule koji se prepoznaje kao logička nula i visoki napon blizu ili na razini napona napajanja koji se prepoznaje kao logička jedinica. Logički krugovi su stoga u osnovi tranzistorske sklopke.

Oscilatore sa logičkim vratima smo već više puta opisivali i tu nema puno mudrosti. Sve se svodi na inverter. Inverter jednu logičku razinu na ulazu pretvara u suprotnu logičku razinu na izlazu. Ako se dakle napravi povratna veza sa izlaza na ulaz invertera, onda će se promijenjeno logičko stanje na izlazu svaki put prenijeti na ulaz, što će uzrokovati ponovnu promjenu stanja na izlazu i tako u krug. Mogli bi reći da logički krug ulazi u vlastito samoosciliranje, a isto se onda može kontrolirati (usporiti) RC elementima (vremenskom konstantom prijenosa signala) u povratnoj vezi. Inverter ili NOT logička vrata se također mogu konfigurirati iz različitih drugih logičkih vrata.

Sada se postavlja pitanje kako onda jedan logički krug spojen u oscilator, poput ovdje prikazanog 7413 koji sadrži dvoja NAND vrata sa četiri ulaza, može procesuirati audio signal sa svim njegovim naponskim i frekvencijskim razinama te ga pretvarati u frekvencijski pomak (devijaciju) osnovne izlazne frekvencije oscilatora. Drugim riječima kako sklop radi kao RF mješač. Očekivali bi da je to sklop koji raspoznaje i procesuira samo dvije logičke razine.

Odgovor na ovo pitanje leži u činjenici da je svaki logički krug sastavljen od tranzistora, dakle sa svim njihovim karakteristikama i koji onda sami po sebi nisu i ne mogu biti u praksi promatrani kao posve savršene sklopke. Idealna tranzistorska sklopka, a time i idealni logički krugovi bi trebali trenutno reagirati na promjenu dva različita stanja i trenutno prebacivati ta dva stanja. U idealnim uvjetima bi zapravo postojale samo dvije razine (nula i Vcc) i ništa između. U praksi naravno ništa ne može biti trenutno (vrijeme nula) nego su potrebna određena vremena trajanja da se procesi unutar tranzistora završe i da time napon postupno poraste ili se smanji s jedne na drugu razinu.

U pravokutnom valnom obliku bočne strane dakle nikad nisu posve vertikalne, nego postoji neki nagib jer skok napona ne može biti trenutan (osim možda u nekom kvantnom svijetu). Ovo smo već opisivali gore u tekstu kod analize signala sa oscilatora Si5351A. Upravo ovo „radno“ područje tranzistora unutar logičkog kruga sa vrlo strmom karakteristikom, može se promatrati kao područje linearnog pojačanja tranzistora. Pojednostavljeno gledano, ovdje se zapravo koristi jedna neželjena karakteristika logičkih sklopki, a to je vrijeme koje potrebno da se napon pojača na logičku jedinicu ili smanji na logičku nulu. U tom vremenu tranzistor radi kao gotovo linearno pojačalo. Iako je to vrijeme vrlo kratko, ono zapravo određuje maksimalnu moguću brzinu rada tranzistora kao sklopke (maksimalnu frekvenciju), te uvelike definira izgled (izobličenje) izlaznog signala.

Više puta smo vidjeli u našim objavama da se ponekad u sklopovima ne koriste određena gotova logička vrata, na primjer inverteri (NOT logička vrata), nego se koriste druga vrata poput NAND ili NOR koja se onda spajaju kao NOT vrata za funkciju oscilatora, bufera i drugo. U našem primjeru pak imamo slučaj da se ne koriste standardna NAND vrata sa dva ulaza, nego NAND vrata sa četiri ulaza, koja su opet spojena kao NAND vrata sa dva ulaza.

Ponekad je razlog za ovo jednostavno taj da se iskoriste oni čipovi koje trenutno imamo na raspolaganju. No u velikom broju slučajeva razlog za to nije tako banalan i leži u samoj unutrašnjoj električnoj shemi logičkih vrata koja se uglavnom sastoje od serijskih i paralelnih kombinacija P-MOS i N-MOS tranzistora. Ponekad jednostavnija logička vrata sa manje ulaza/izlaza mogu imati složeniju elektroničku shemu od logički složenijih vrata. Tako se kombinacijama pojedinih različitih logičkih krugova mogu dobiti neka logička vrata boljih električnih karakteristika nego da je upotrijebljen čip sa baš tim vratima. Karakteristike se najviše očituju u većoj brzini, manjoj struji curenja, manjoj potrošnji struje, boljim ulaznim i izlaznim impedancijama i slično.

Elektroničari koji se dugo bave logičkim elektroničkim sklopovima raspoznaju u praksi određene razlike glede tvorničke konstrukcije pojedinih logičkih vrata. Ovo najčešće nema značaj za primjenu u većini digitalnih krugova, no za neke specifične primjene te razlike u unutrašnjoj konstrukciji i električnim specifikacijama pojedinih logičkih vrata mogu biti od velikog značaja.

Logički integrirani krug SN7413 za našu primjenu bi morao raditi na frekvenciji 25 MHz, a to je već blizu granične frekvencije i za brze TTL logičke čipove. Stoga mi ovdje obavezno moramo koristiti brze inačice ovog čipa sa oznakom LS ili F (74LS13, 74F13). Najbrža je inačica 74F13 no taj čip je teško nabaviti pa nam preostaje 74LS13.

U zalihama imamo dva čipa SN74LS13N proizvođača Motorola iz 1988. godine, jedan čip SN7413N Texas Instruments iz 1973. godine, a naručili smo još pet novih čipova SN74LS13N iz Kine. Test je pokazao da su granične frekvencije rada ovih čipova u rasponu 23-26 MHz. Jedan čip iz Kine je detektiran kao neispravan jer doseže jedva 20 MHz i pokazuje velike nestabilnosti u spoju oscilatora kroz čitav opseg frekvencija. Ostali čipovi iz Kine, kao i Motorola čipovi su približno istih karakteristika. Najviše je iznenadio čip Texas Instrumentsa koji je najstariji, rabljen (odnekud izvađen), koji čak i nema oznaku LS (ili neku drugu) i koji je stabilno radio na frekvenciji preko 26 MHz, dakle višoj od svih ostalih čipova.

Kako god bilo, ovo su i dalje granične frekvencije i vjerojatno nije pametno koristiti ove čipove za oscilatore na 25 MHz. Srećom, signal iz ovakvih relaksacijskih oscilatora je bogat harmonicima tako da nema nikakve zapreke koristiti drugi harmonik osnovne frekvencije 12,5 MHz.

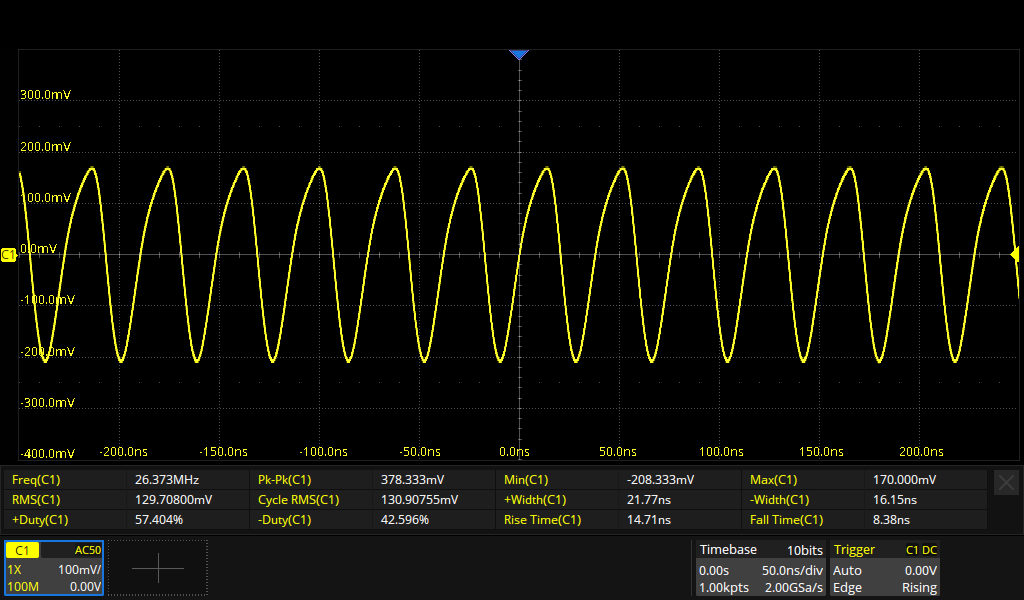

Čip Texas Instrumentsa iz 1973. godine pokazao je najveću brzinu u radu. Signal na rubnom području rada „pravokutnog“ oscilatora je uvijek „šiljast“ i varljivo izgleda slično sinusnom signalu. To je zato jer do izražaja dolaze bočne strmine čije je vrijeme porasta i pada dulje od vremena trajanja „ravnog“ dijela signala. Međutim, iako je nalik sinusnom, ovo je i dalje harmonicima vrlo bogat signal.

Čip Texas Instrumentsa iz 1973. godine pokazao je najveću brzinu u radu. Signal na rubnom području rada „pravokutnog“ oscilatora je uvijek „šiljast“ i varljivo izgleda slično sinusnom signalu. To je zato jer do izražaja dolaze bočne strmine čije je vrijeme porasta i pada dulje od vremena trajanja „ravnog“ dijela signala. Međutim, iako je nalik sinusnom, ovo je i dalje harmonicima vrlo bogat signal.

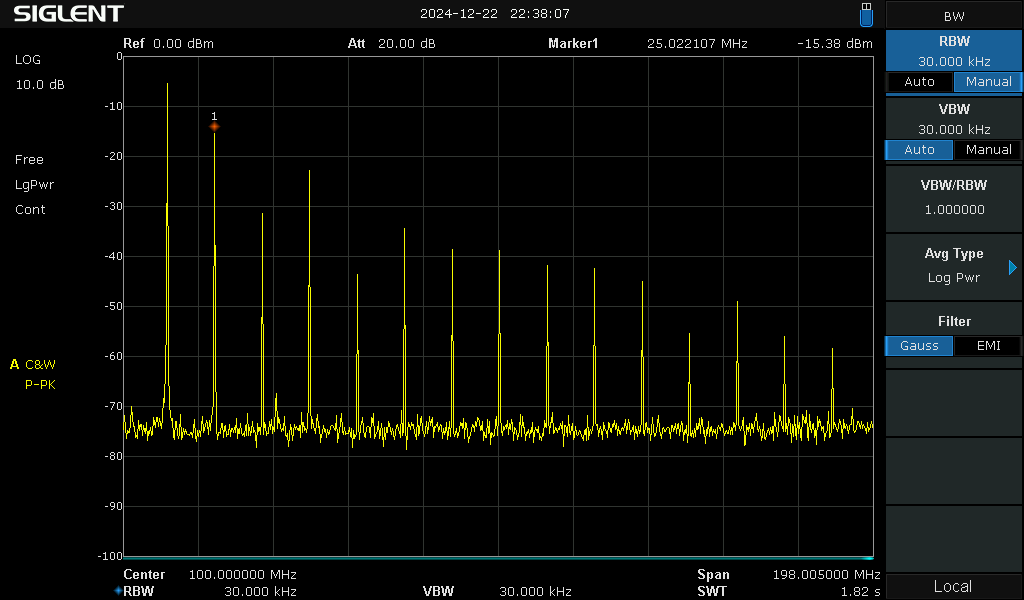

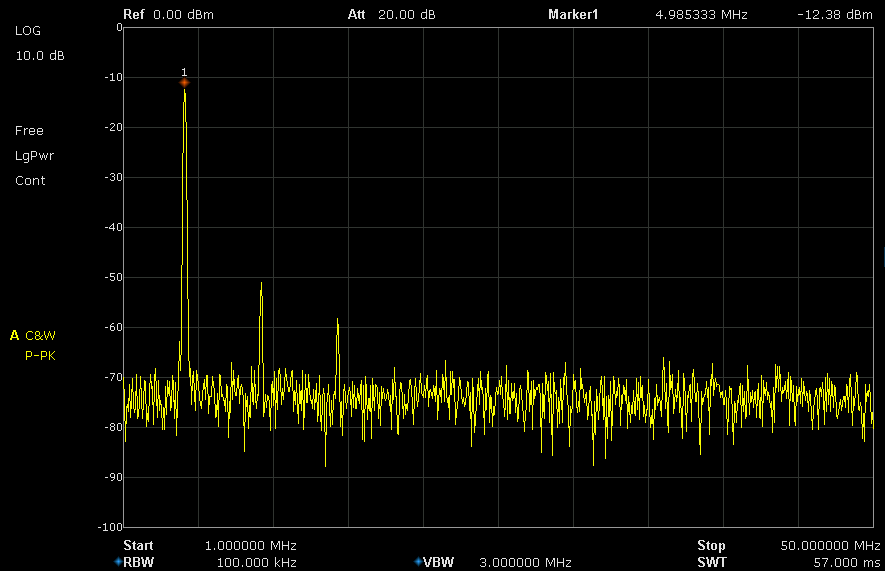

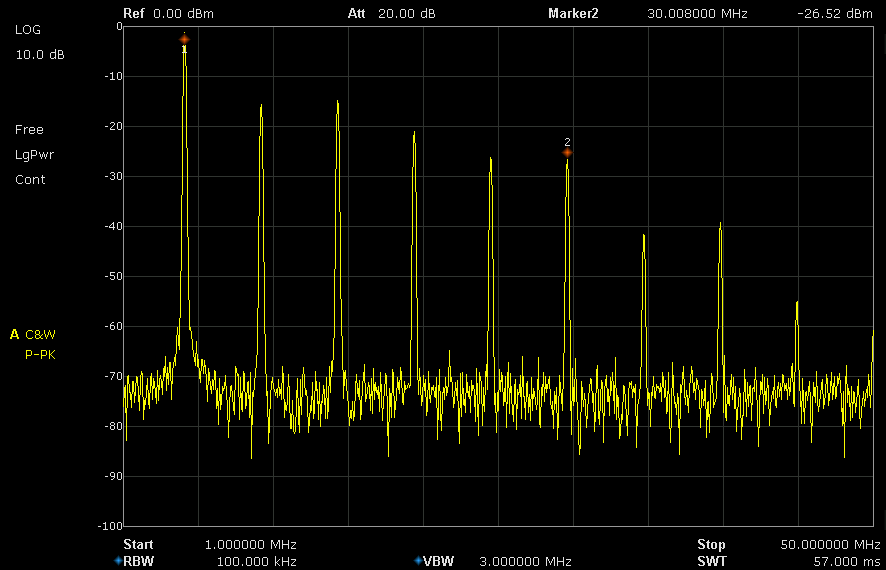

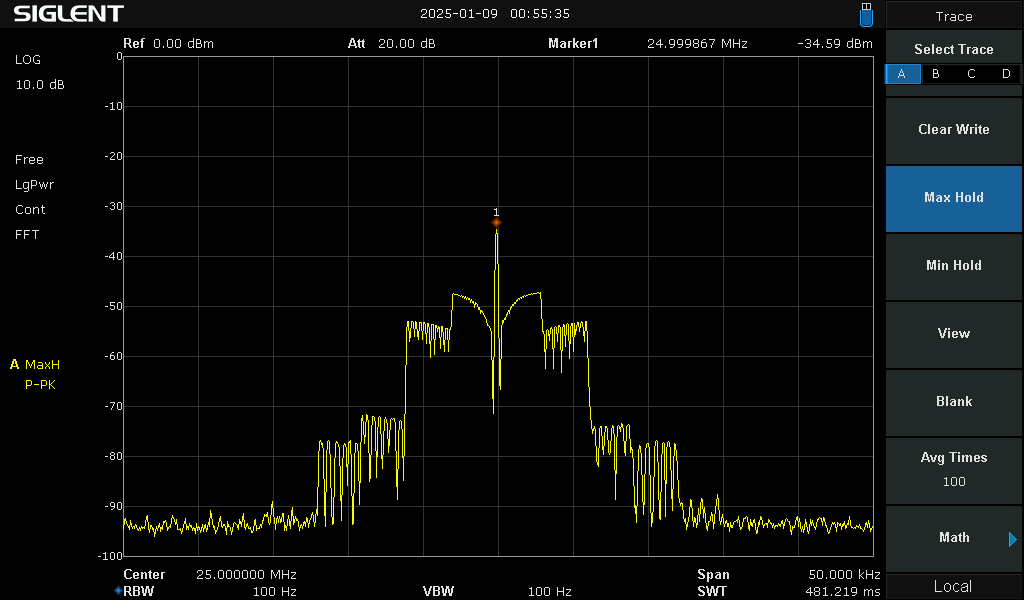

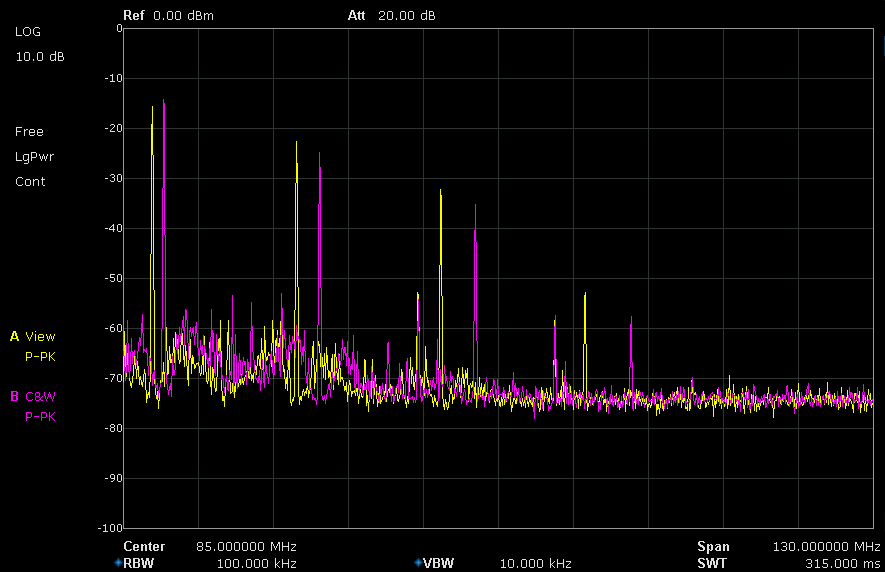

Spektralna slika signala iz oscilatora 12,5 MHz sa logičkim čipom SN74LS13. Vidi se daje drugi harmonik na 25MHz samo nekih 10 dBm slabiji od osnovnog signala čime je posve upotrebljiv za naš projekt.

Spektralna slika signala iz oscilatora 12,5 MHz sa logičkim čipom SN74LS13. Vidi se daje drugi harmonik na 25MHz samo nekih 10 dBm slabiji od osnovnog signala čime je posve upotrebljiv za naš projekt.

U konačnici, testirali smo kako radi naša shema sa čipom SN74LS13 kao stvarni FM predajnik. Radi iznenađujuće dobro. Jasno da izobličenja ima što je posve za očekivati jer uz noseći signal pun harmonika ne koristimo nikakve filtre, no sve u svemu lijepo možete čuti čak i 8. harmonik na 100 MHz (koji pada u radiodifuzni FM opseg) na udaljenosti nekoliko desetaka metara.

Plan za dalje je zalemiti ovaj modulator na tiskanu pločicu, izraditi neki jednostavni pojasni filtar za 25 MHz i onda testirati rad Si5351A sa ovim modulatorom. Isto tako nećemo odustati ni od kristalnog oscilatora/modulatora. Naručiti ću kristalni oscilator (rezonator) na 5 MHz i vidjeti može li se izdvojiti 5. harmonik. Ovo bi bilo najbolje rješenje, ne samo zbog stabilnosti, nego i zbog toga što bi isti kristal koristili za obje namjene (FM modulaciju i AM modulaciju). To bi isključilo potrebu za osmišljavanjem mehaničkih ili elektroničkih sklopki za preklapanje XA (takt) ulaza za Si5351A što uvijek može rezultirati šumovima i smetnjama koje degradiraju ili blokiraju rad našeg VFO-a.

FM modulacija kristalnih oscilatora

Već smo rekli da su kristalni oscilatori frekvencijski vrlo stabilni i teško je vanjskim elementima izazvati neku veliku devijaciju (pomak) frekvencije od one na kojoj rezonira sam kristal, svakako ne ni blizu pomak od ±75 kHz koliko bi trebalo za komercijalni WFM radio. Stoga je potrebno početnu malu devijaciju frekvencije kristala koja se još može izazvati (do nekoliko kHz) pojačati dodatnim stupnjevima umnožavanja frekvencije ili korištenjem harmoničkih frekvencija.

Odabir kristala

Za naš projekt smo naručili iz Kine jeftine kristale opće namjene od 5 MHz iz DIP HC-49S serije. Navedenu seriju odlikuje nizak ESR što pridonosi stabilnosti frekvencije ali i povećan „pullability“ što znači da je vanjskim kapacitetima moguće nešto više razvući raspon rezonantnih frekvencija kristala.

Već ste primijetili da u mojim objavama maksimalno izbjegavam detaljna teoretska objašnjavanja i složene izračune za objašnjenje rada nekog elektroničkog elementa ili sklopa. Preferiram upotrebu gotovih kalkulatora i simulatora elektroničkih krugova, no glede toga razlika između idealnih i stvarnih elektroničkih komponenti može biti značajna, pogotovo ako koristimo jeftine komponente opće namjene iz masovne proizvodnje. Stoga je bolje analizirati realne praktične snimke signala iz pojedinih sklopova gdje se onda izravno uočavaju stvarne karakteristike promatranih elemenata i sklopova. Objašnjenja pokušavam svesti na razinu osnovnog shvaćanja nekog principa ili pojave. Tako ćemo uraditi i za naš kristal.

Frekvencijsko-impedancijska karakteristika kristala

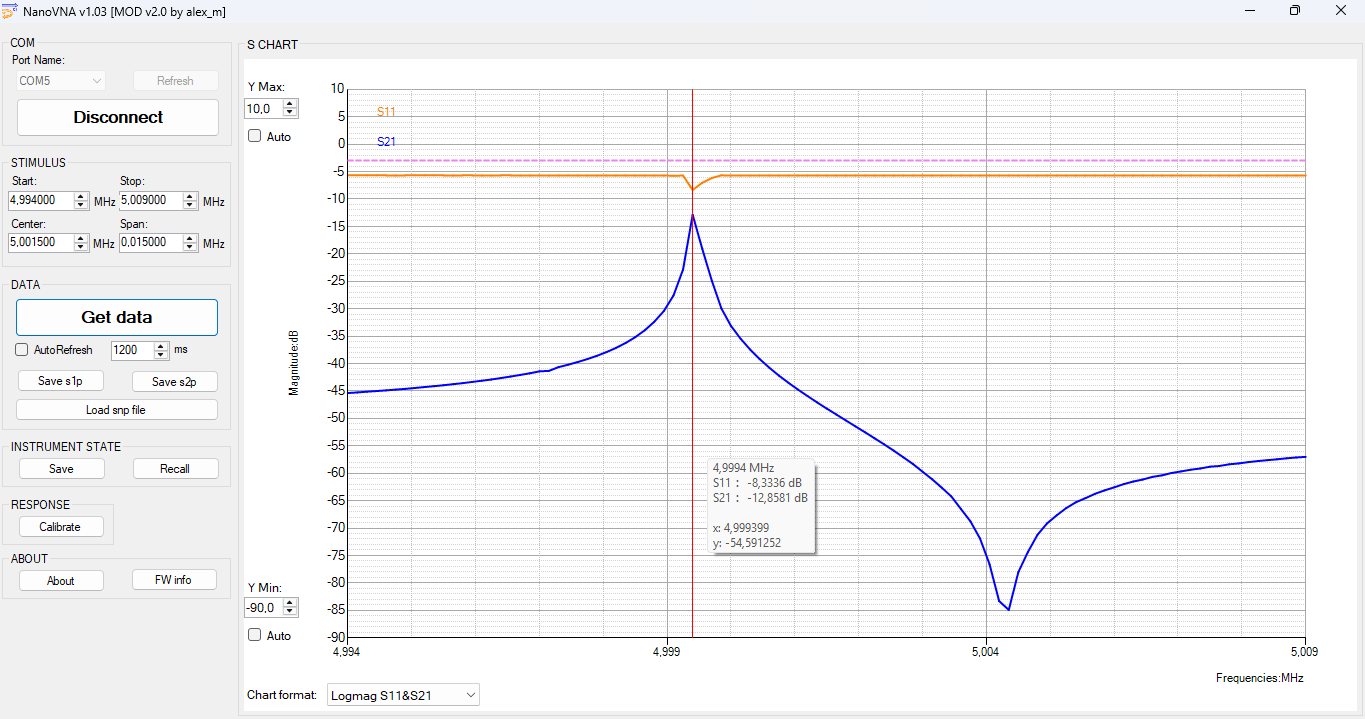

Za početak ćemo analizatorom spektra snimiti frekvencijsko-amplitudnu (impedancijsku) karakteristiku naših kristala. Ona će nam pokazati rezonantnu krivulju istih.

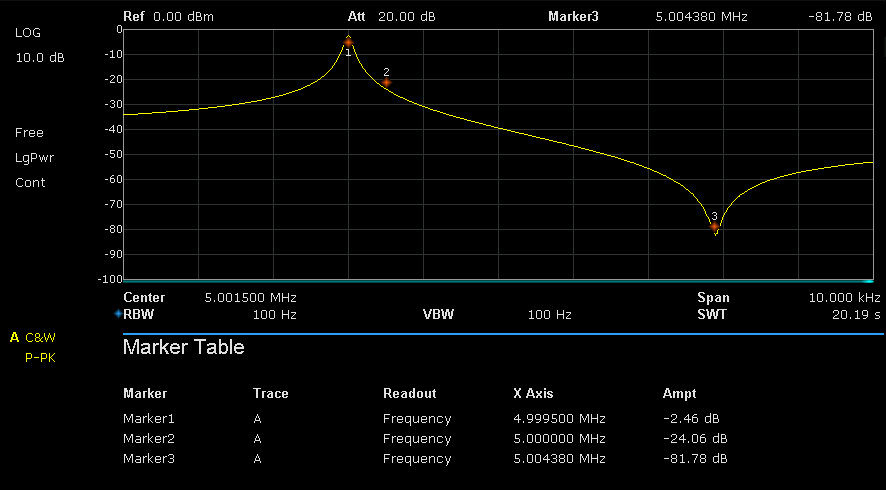

Na frekvencijsko-amplitudnoj karakteristici kristala od 5 MHz jasno se uočavaju dvije rezonancije: serijska na 4,999500 MHz (Marker 1) i paralelna na 5,004380 MHz (Marker 3). Deklarirana frekvencija od 5 MHz se nalazi negdje u sredini bliže serijskoj rezonantnoj frekvenciji.

Na frekvencijsko-amplitudnoj karakteristici kristala od 5 MHz jasno se uočavaju dvije rezonancije: serijska na 4,999500 MHz (Marker 1) i paralelna na 5,004380 MHz (Marker 3). Deklarirana frekvencija od 5 MHz se nalazi negdje u sredini bliže serijskoj rezonantnoj frekvenciji.

Na frekvencijsko-impedancijskoj karakteristici kristala od 5 MHz vrlo lijepo se vidi da kristal pokazuje dvije oštre rezonantne frekvencije iznad i ispod 5 MHz, na međusobnom razmaku od 4,880 kHz. Vidimo da je prva rezonantna frekvencija na vrlo niskoj impedanciji (gušenje svega -2,5 dB), odnosno praktično teži prema kratkom spoju. To nas odmah upućuje na zaključak kako je ovdje riječ o serijskoj rezonanciji kod koje otpor LC titrajnog kruga pada praktički na nulu. Druga rezonantna frekvencija pak je na najvišoj točki impedancije (najveći otpor, gušenje -82 dB) što nam ukazuje kako je ovdje riječ o paralelnoj rezonanciji kod koje otpor LC titrajnog kruga teži biti beskonačan (otvoren strujni krug).

S obzirom da kristal dakle pokazuje obje rezonantne frekvencije, onda ga svakako možemo promatrati kao kombinaciju paralelnog i serijskog LC titrajnog kruga.

Nadomjesna shema kristala: Ls – induktivna komponenta kristala, Cs – kapacitivna komponenta kristala, Rs – omski otpor kristala (ESR), Cp – paralelna kapacitivna komponenta koju predstavlja unutrašnji kapacitet i vanjske električne veze kristala

Nadomjesna shema kristala: Ls – induktivna komponenta kristala, Cs – kapacitivna komponenta kristala, Rs – omski otpor kristala (ESR), Cp – paralelna kapacitivna komponenta koju predstavlja unutrašnji kapacitet i vanjske električne veze kristala

Iz nadomjesne sheme kristala možemo vidjeti kako je on u osnovi serijski LC titrajni krug, no kao realni element neophodno ima i neki svoj omski otpor kao i interni paralelni kapacitet koji je nemoguće izbjeći zbog same konstrukcije kristala. Prema tvorničkim podacima, ESR za naš kristal je 80-150 Ω maksimalno, a interni ili shunt kapacitet je maksimalno 7 pF. O veličini tog internog kapaciteta ovisi paralelna rezonantna frekvencija pa možemo reći da ona nastaje kao posljedica parazitskih kapaciteta u konstrukciji kristala koji se ne mogu izbjeći. Stoga se kod konstrukcije kristalnih oscilatora teži da kristal radi na svojoj serijskoj rezonanciji jer je tu manja osjetljivost na vanjske parazitske kapacitete.

Da bi vidjeli koja reaktancijska komponenta (induktivna ili kapacitivna) prevladava na određenim frekvencijama, moramo snimiti frekvencijsko-faznu karakteristiku našeg kristala.

Frekvencijsko-fazna karakteristika kristala

Inače posjedujem vrlo dobar analizator spektra (Siglent SSA3021X) preko kojeg smo snimili rezonantne frekvencije kristala, no analizatori spektra ne mogu snimati fazne vektore. Za to nam je potreban VNA (vector network analyzer). Oba ova instrumenta snimaju karakteristike u frekvencijskoj domeni, no analizator spektra to radi s obzirom na amplitudu, a VNA s obzirom na fazu promatranog signala.

Osciloskop, analizator spektra i VNA su tri osnovna instrumenta za promatranje i mjerenje električkih signala. Ponuda sva tri instrumenta je danas vrlo bogata, a cjenovni rasponi idu od nekoliko desetaka eura do nekoliko desetaka tisuća eura. Jasno je dakle da postoje ogromne razlike u specifikacijama i mogućnostima između pojedinih modela ovakvih mjernih instrumenata.

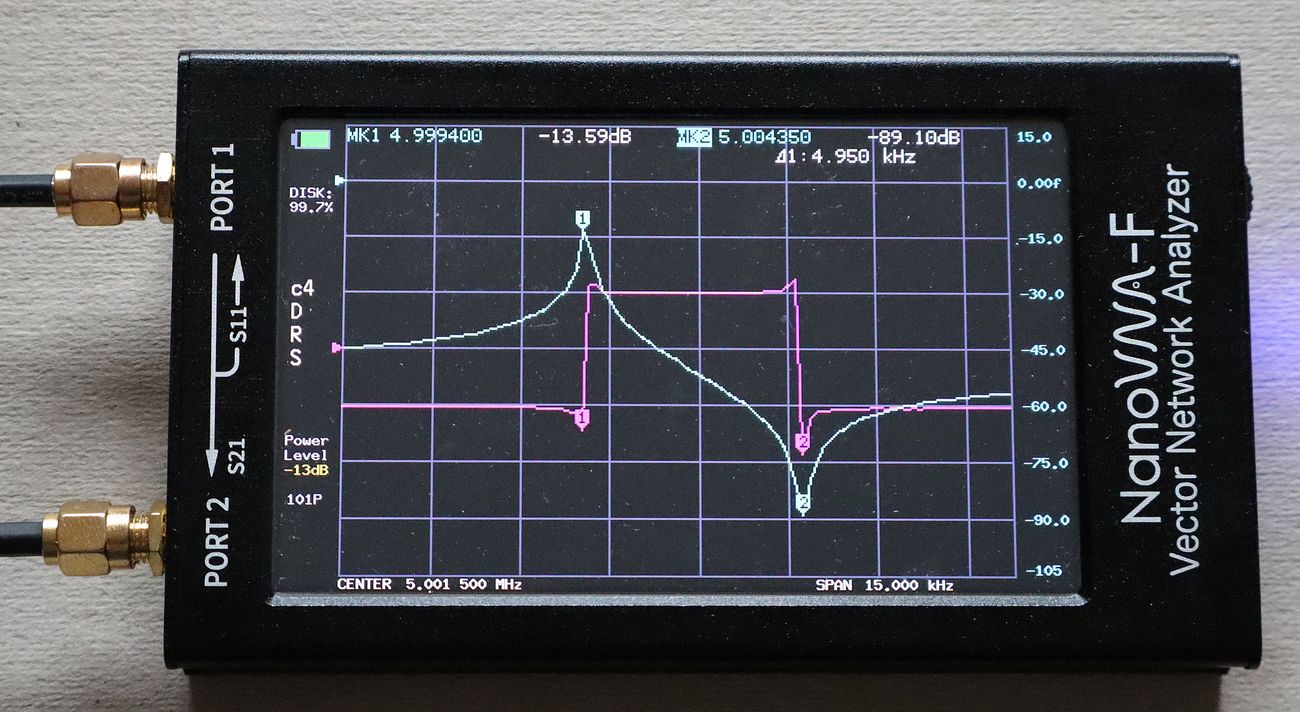

Moj VNA spada u kategoriju najjeftinijih na tržištu i riječ je o popularnom modelu iz serije NanoVNA-F. Kod jeftinijih VNA ograničenja su u ulaznoj osjetljivosti i razini vlastitog šuma (dinamički raspon), no također i u brzini rada, rezoluciji mjerenja (broj točaka) i rezoluciji prikaza (displej). Ograničenja su naravno i u mogućnostima analize i usporedbe snimljenih signala bilo u realnom vremenu ili naknadno kao i u dostupnim kontrolama. Takvi uređaji obično imaju samo osnovne kontrole i osnovne analize snimljenih signala. Pa pak, današnji VNA cjenovnog razreda do 150 eura posve zadovoljavaju svim amaterskih zahtjevima i za tu cijenu zapravo imaju impresivne specifikacije i mogućnosti mjerenja.

Ovdje se vidi fotoaparatom slikan ekran NanoVNA-F tijekom mjerenja amplitudne i fazno-frekvencijske karakteristike kristala. Iako je slika uživo puno bolja što se tiče boja i oštrine, već i ovdje se lako uočava prilično niska rezolucija mjerenja. Maksimalna brzina mjerenja ne 200 točaka u sekundi, a maksimalna rezolucija mjerenja je 800 točaka. Displej je rezolucije 800×480 točaka. Iako ovi podaci nišu baš impresivni to je i dalje prilično iskoristiv mjerni instrument u praksi.

Ovdje se vidi fotoaparatom slikan ekran NanoVNA-F tijekom mjerenja amplitudne i fazno-frekvencijske karakteristike kristala. Iako je slika uživo puno bolja što se tiče boja i oštrine, već i ovdje se lako uočava prilično niska rezolucija mjerenja. Maksimalna brzina mjerenja ne 200 točaka u sekundi, a maksimalna rezolucija mjerenja je 800 točaka. Displej je rezolucije 800×480 točaka. Iako ovi podaci nišu baš impresivni to je i dalje prilično iskoristiv mjerni instrument u praksi.

Softver koji dolazi uz NanoVNA-F je prilično jednostavan, spor i sa osnovnim mogućnostima. Praktično omogućuje samo povezivanje sa NanoVNA-F preko USB porta (emulacija COM porta) u cilju razmjene .s1p i .s2p datoteka. To su osnovi tekstualne datoteke kojima se prenose rezultati mjerenja, odnosno vrijednosti X i Y osi grafova. Stoga softver ne može komunicirati sa NanoVNA-F u realnom vremenu i ne može kopirati prikaz na ekranu. Postoji puno programa namijenjeni za čitanje .s1p i .s2p datoteka i crtanje grafova iz istih, a u tu svrhu može poslužiti i MS Excel ili bilo koji drugi slični program sa podrškom za XY grafove.

Mi ovdje imamo problem jer želimo istovremeni prikaz amplitudne i fazne karakteristike, dakle želimo usporediti dva frekvencijska grafa sa različitim mjernim jedinicama na Y osi (dBm za amplitudu i stupnjevi za fazni pomak). Ovakav prikaz radi na samom NanoVNA-F displeju (iako se na Y osi može odabrati za prikaz samo jedna mjerna vrijednost), no originalni softver ne podržava učitavanje takvih kombinacija. Nakon nekoliko instalacija različitih drugih softvera za .s1p i .s2p datoteke, nisam uspio naći ni jedan koji može napraviti tu kombinaciju, barem ne u besplatnoj inačici. Stoga sam se poslužio dobrom starim MS Excelom i ručno preklopio ta dva frekvencijska grafa.

Pomoću instrumenta NanoVNA-F snimili smo .s1p datoteke sa rezultatima mjerenja amplitudnog i faznog odziva našeg kristala. Datoteke smo zatim obradili u MS Excelu kako bi dobili paralelni usporedni prikaz ove dvije frekvencijske karakteristike.

Pomoću instrumenta NanoVNA-F snimili smo .s1p datoteke sa rezultatima mjerenja amplitudnog i faznog odziva našeg kristala. Datoteke smo zatim obradili u MS Excelu kako bi dobili paralelni usporedni prikaz ove dvije frekvencijske karakteristike.

Na frekvencijama nižim od serijske rezonantne frekvencije (4,999500 MHz) zakretanje faze signala je oko -90° što znači da kristal ovdje ima vrlo izraženu kapacitivnu komponentu impedancije. Na serijskoj rezonantnoj frekvenciji dolazi do nagle promjene faze za 180° tako da ona od ove točke iznosi +90°. To znači da kristal ovdje pokazuje izraženu induktivnu komponentu. Na paralelnoj rezonantnoj frekvenciji (5,004380 MHz) ponovno dolazi do naglog okretanja faze za 180° i ona od ove točke opet iznosi -90° što znači da do izražaja ponovno dolazi kapacitivna komponenta kristala.

Ovo vrlo naglo zakretanje faze sa praktično čisto kapacitivne (-90°) na čisto induktivnu reaktanciju (+90°) je specifičnost kristala koja određuje njegove vrlo oštre rezonantne krivulje. To zakretanje će se uvijek događati na rezonantnoj frekvenciji bez obzira koliko ju pomaknemo vanjskim kapacitetima.

Promjena rezonantnih frekvencija kristala

Iz svega je jasno da ćemo dodavanjem vanjskih (dodatnih) kondenzatora ili zavojnica u seriju ili paralelno sa kristalom promijeniti njegovu rezonantnu serijsku ili paralelnu frekvenciju. Praktičnije je dodavanje kondenzatora (promjenjivih kondenzatora) umjesto zavojnica jer su jednostavnije i manje konstrukcije. Dodavanje vanjskog kapaciteta će imati najveći učinak u dijelu gdje se naglašenost kapacitivne komponente, nakon rezonancije (podjednaka impedancija obje komponente), počinje mijenjati u induktivnu komponentu, dakle u području između dvije rezonancije, bliže serijskoj rezonanciji. Ovdje je dovoljan već mali dodatni kapacitet da se promjeni frekvencija kristala.

Teoretski se čini kako bi neki dovoljno veliki kapacitet ili induktivitet mogao promijeniti rezonantnu frekvenciju kristala bilo gdje daleko od njegovih osnovnih rezonancija. Međutim, kristal se ne smije opteretiti velikim kapacitetima ili induktivitetima jer se time povećava disipacija snage na njemu. To dovodi do zagrijavanja kristala što je vrlo neželjen učinak jer su kristali temperaturno osjetljivi elementi kojima promjena temperature izaziva pomak rezonantnih frekvencija. U slučaju pretjeranog opterećenja kristal može biti i uništen. Prema podacima za naš kristal disipacija snage na njemu može biti u granicama 1-500 µW (tipično 100 µW). Također, vanjski kapaciteti ili induktiviteti neminovno ruše faktor dobrote kristala i rezonancije postaju šire sa većim gubicima. To je još jedan razlog zašto dodavanje velikih kapaciteta kristalima nije dobra ideja.

Vrijednosti kondenzatora koji se stavljaju paralelno kristalu ovise o više faktora, a između ostalog i o samim karakteristikama upotrijebljenog kristala. Stoga se najbolje pridržavati tvorničkih uputa za određeni tip i frekvenciju kristala. U svakom slučaju, idealno bi bilo precizno izmjeriti frekvenciju oscilatora sa određenim kristalom, a onda kondenzatorima dovesti tu frekvenciju na nominalnu vrijednost koja je naznačena na samom kristalu. U praksi se vrijednosti tih kondenzatora mogu kretati u rasponu od 3 pF do 2200 pF što najviše ovisi o samoj frekvenciji i tipu kristala. Za naš kristal od 5 MHz se specificira dodavanje serijskog kondenzatora 16-32 pF.

Koja frekvencija je ispisana na samom kristalu

Sad dolazimo do zanimljivog pitanja: ako kristal ima dvije rezonantne frekvencije koje se obaveznim dodatkom vanjskih kapaciteta dodatno pomiču, koja je onda to nominalna frekvencija ispisana na samom kristalu.

Proizvođači na kristalima obično otisnu samo jednu rezonantnu frekvenciju (najčešće serijsku), no u tvorničkim podacima svakako treba biti navedeno koja frekvencija je otisnuta jer razlika između serijske i paralelne rezonancije kristala može biti i nekoliko kHz. Štoviše, na kristal se najčešće ne otiskuje njegova točna (stvarna) serijska ili paralelna rezonantna frekvencija, nego frekvencija na kojoj će oscilator sa tim kristalom oscilirati kada mu se dodaju obavezni vanjski kondenzatori (loading capacitance) i čiju vrijednost također propisuje proizvođač. Tako je slučaj i sa našim kristalom nominalne vrijednosti 5 MHz. Vidjeli smo da je njegova serijska rezonantna frekvencija zapravo nešto niža (za 500 Hz), a isto se onda kompenzira i ugodi dodavanjem vanjskog kapaciteta 16-32 pF.

No, ni takvo označavanje kristala nije uvijek pravilo u praksi. Kao što smo vidjeli u objavi Generator 50 MHz RIZ u praksi se kristali mogu označavati na različite načine. Za overtonski brušene kristale (koji osim na osnovnoj rezoniraju i na harmoničkim frekvencijama) može biti upisana neka overtonska (viša harmonična) frekvencija, ovisno o krugu za koji je kristal namijenjen. Također, ponekad se upisuje ona frekvencija koja ni približno ne odgovara niti jednoj rezonantnoj frekvenciji kristala, nego izlaznoj frekvenciji specifičnog kruga koji se bazira na određenom kristalu. To se u prvom redu odnosi na superheterodinske RF krugove gdje može biti upisana frekvencija koja je uvećana ili umanjenja za vrijednost heterodinske međufrekvencije.

Frekvencije se vrlo često upisuju u skraćenom brojčanom obliku bez mjerne jedinice (kHz, MHz). Na nekim kristalima ćemo umjesto oznake frekvencije naći samo oznaku kanala nekog primopredajnika za koji je taj kristal predviđen. Stoga, ukoliko imamo neki kristal kojem ne znamo porijeklo ni očekivanu frekvenciju, a ista nije u cijelosti ispisana na tijelu kristala, teško ćemo iz same oznake moći zaključiti točne rezonantne frekvencije kristala, pogotovo ako ne znamo ni tip kristala.

Zašto se kristalima uvijek dodaju vanjski kapaciteti

Zašto je uopće neophodno dodavati te vanjske kondenzatore kristalima za podešavanje rezonantne frekvencije. Za to ima više razloga. U praksi kristalni oscilatori ne mogu stabilno raditi na točnim serijskim i paralelnim rezonancijama kristala nego obično negdje između te dvije vrijednosti. Kristali se stavljaju u pozitivnu povratnu spregu oscilatora koja vrši određeni utjecaj na kristal, a često je potrebno i galvansko odvajanje istosmjerne od izmjenične komponente tako da je serijsko dodavanje kondenzatora samim time neophodno. Oscilator za stabilan i ispravan rad treba povratnu vezu u fazi, a s obzirom da elektronički elementi nisu savršeni to je teško postići. Stoga je opet neophodno dodavati vanjske kapacitete ili induktivitete za kompenzaciju faznog pomaka. Ovo će biti jasnije ako nacrtamo dvije osnovne sheme kristalnih oscilatora. Najčešća izvedba oscilatora koji koristi serijsku rezonanciju kristala je Pierce oscilator, a za paralelnu rezonanciju je to Colpitts oscilator.

Colpitts i Pierce kristalni oscilatori

Tipične shema Colpitts oscilatora sa paralelnom rezonancijom kristala i Pierce oscilatora sa serijskom rezonancijom kristala.

Tipične shema Colpitts oscilatora sa paralelnom rezonancijom kristala i Pierce oscilatora sa serijskom rezonancijom kristala.

Sheme dva tipična kristalna oscilatora namjerno smo nacrtali tako da se jasno vidi kako se oba baziraju na tranzistorskom pojačalu i kristalom u pozitivnoj povratnoj sprezi (veza sa izlaza pojačala natrag na ulaz pojačala). Također u oba slučaja vidimo da su kondenzatori u povratnoj sprezi neophodni kako ne bi nastao kratak spoj u istoj. U primjeru Colpitts oscilatora sa paralelno vezanim kristalom to bi bio izravan kratki spoj, a u slučaju Pierce oscilatora na serijskoj rezonanciji impedancija kristala je vrlo niska (praktično nekoliko oma) što bi dovelo do prejake povratne sprege i nestabilnosti oscilatora.

Osim toga, kondenzatori su neophodni i za stabilan rad kristalnog oscilatora glede povratne faze, odnosno služe za dobivanje ispravnog faznog pomaka u pozitivnoj povratnoj sprezi. Znamo da za stabilan rad oscilatora ulazni signal dobiven preko povratne veze mora biti potpuno u fazi sa izlaznim signalom (0° ili 360°). Što je odstupanje u fazi veće to će efikasnost (jačina) i stabilnost oscilatora biti manja.

Kod Colpitts oscilatora tranzistor radi kao emitersko slijedilo gdje je teoretski izlazni signal u fazi sa ulaznim. To znači da u povratnoj vezi moramo izbjeći promjenu faze. No, kako smo rekli, kristal sam po sebi na rezonantnoj frekvenciji stvara pomak faze od 180° tako da su neophodni kondenzatori na svakom kraju kristala koji će stvarati dodatan pomak faze za 180° (2 x 90°) i time vratili signal na istu fazu. U praksi, sa stvarnim elementima oscilatora, ta zakretanja faze nisu idealna (točno 90°). Razlog za to su naravno parazitske reaktivne komponente koje čine impedanciju LC elemenata, no tu je i procesuiranje signala u samom pojačalu. Kod realnog pojačala uvijek postoji neko malo kašnjenje između ulaznog i izlaznog signala iz pojačala (tranzistora, invertera) za vrijeme koliko je potrebno da se signal procesuira. To kašnjenje onda naravno stvara određeni pomak faze koji je u povratnoj sprezi potrebno kompenzirati serijskim kondenzatorima.

Kod Pierce oscilatora pak tranzistor radi kao klasično pojačalo sa zajedničkim emiterom i signal se uzima sa kolektora koji je onda teoretski za 180° fazno pomaknut od ulaznog signala. S obzirom da i sam kristal stvara pomak faze 180° teoretski na ulazu u pojačalo dobivamo signal u fazi sa izlaznim. Međutim, zbog opisanih nesavršenosti elementa koji čine oscilator i ovdje pomaci faze neće biti idealni tako da je potrebna kompenzacija kondenzatorima. Također, serijska rezonancija na kojoj radi kristal u Pierce oscilatoru uzrokuje vrlo nisku impedanciju u pozitivnoj povratnoj sprezi, te se jačina te sprege mora kontrolirati vanjskim kondenzatorima. Pierce oscilatori stoga ne mogu raditi na pravoj serijskoj ili paralelnoj rezonanciji kristala. Djeluju negdje između dvije vrijednosti, ali to je gotovo uvijek bliže serijskoj nego paralelnoj rezonanciji (kako smo i vidjeli na gornjem snimku) jer se teži dodavanju kapaciteta što manjih vrijednosti kako se kristal ne bi nepotrebno opterećivao.

Efekt dodanih kondenzatora na promjenu rezonantnih frekvencija kristala

Iz izmjerenih karakteristika kristala i osnovnih objašnjenja je jasno da serijsku rezonanciju kristala možemo mijenjati serijskim dodavanjem kondenzatora kristalu, a paralelnu rezonanciju kristala možemo mijenjati paralelnim dodavanjem kondenzatora kristalu. U prvom slučaju, što je serijski dodan kondenzator veće vrijednosti, serijska rezonantna frekvencija će se pomaknuti prema više. Isto tako, što je paralelno spojeni kondenzator veće vrijednosti, to će se paralelna rezonantna frekvencija pomaknuti prema niže.

Iz ovoga pak proizlazi da frekvenciju kristala možemo mijenjati u rasponu frekvencija između serijske i paralelne rezonancije, dakle u našem slučaju između 4,999500 MHz i 5,004380 MHz što je raspon od 4,880 kHz. Praktično vjerojatno nećemo moći postići toliku devijaciju jer bi trebali kondenzatore velikog kapaciteta koji onda previše opterećuju kristal i negativno djeluju na njegov faktor dobrote.

Prvo ćemo napraviti malu testnu pločicu da vidimo kolika je devijacija frekvencije uopće moguća sa našim kristalima. Promjenjivi kondenzatori ne bi trebali biti većeg kapaciteta od 32 pF jer je to maksimalno dozvoljeno opterećenje prema tvorničkim specifikacijama, a osim toga i kapacitivne diode koje mislimo koristiti za FM modulaciju imaju maksimalni kapacitet od nekih 38 pF (BB 910). Naravno, serijski kapacitivnoj diodi se mora dodati i fiksni kondenzator male vrijednosti za odvajanje upravljačkog (audio) napona niske frekvencije, od frekvencije rada oscilatora na 5 MHz. Time će ukupni kapacitet modulacijskog kapacitivnog kruga biti manji što možemo popraviti upotrebom više paralelno spojenih kapacitivinih dioda. U zalihama imamo promjenjive kondenzatore 3-150 pF pa ćemo ih iskoristiti za naš test. Uglavnom, naš „univerzalni“ testni krug izgleda ovako.

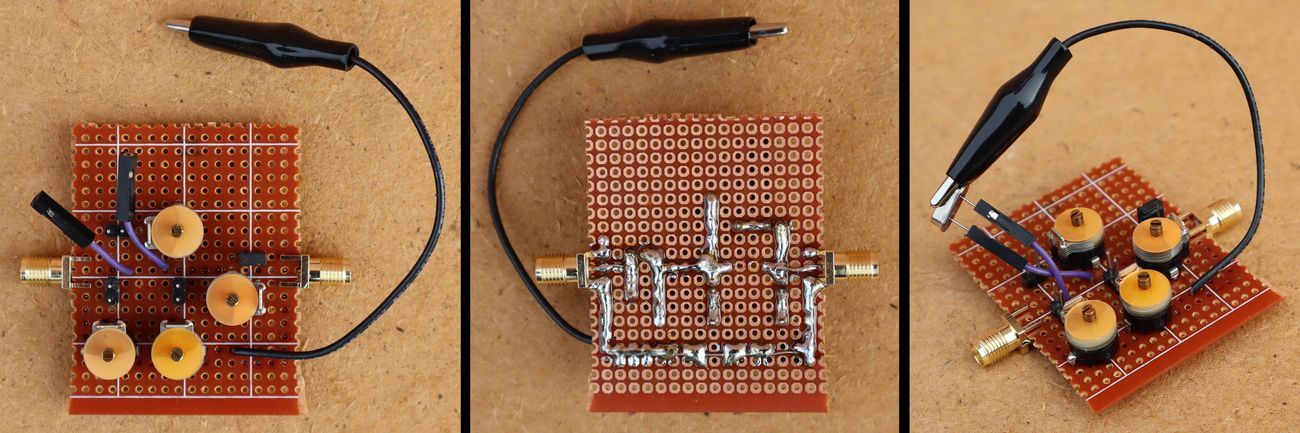

Testni krug za simulaciju kombinacija kristala i kondenzatora u povratnim vezama različitih kristalnih oscilatora. Metalno kućište kristala smo uzemljili jer je bez toga kristal osjetljiv na vanjske parazitske kapacitete (dodir prstom može promijeniti interne kapacitete za nekoliko pF). Također, svakom trimer-kondenzatoru je dodan kratkospojnik kako bi mogli kontrolirati njegovo uključivanje ili isključivanje iz mjernog kruga.

Testni krug za simulaciju kombinacija kristala i kondenzatora u povratnim vezama različitih kristalnih oscilatora. Metalno kućište kristala smo uzemljili jer je bez toga kristal osjetljiv na vanjske parazitske kapacitete (dodir prstom može promijeniti interne kapacitete za nekoliko pF). Također, svakom trimer-kondenzatoru je dodan kratkospojnik kako bi mogli kontrolirati njegovo uključivanje ili isključivanje iz mjernog kruga.

Test je pokazao da serijski vezani kondenzator do 150 pF može povećati serijsku rezonantnu frekvenciju za 1,107 kHz. Isti takav paralelno vezani kondenzator pak može smanjiti paralelnu rezonantnu frekvenciju za 4,788 kHz odnosno praktično za čitav raspon između serijske i paralelne rezonantne frekvencije. Međutim, kako smo već objašnjavali, veliki kapacitet narušava faktor dobrote kristala tako da se amplituda sa početnih -82 dB na najnižoj frekvenciji povećala na -30 dB.

Koliku FM devijaciju želimo postići

Cilj našeg testnog predajnika svakako nije pokrivanje komercijalnog FM UKV opsega signalom velike kvalitete (devijacija ±75 kHz) jer tu uvijek radi puno lokalnih postaja i dodatne testne emisije nisu potrebne. Na kraju krajeva, (jedino) taj opseg i nije zanimljiv za naše svrhe.

Za sve druge službene i radioamaterske veze uskopojasnom FM modulacijom (NFM) gdje se prenosi govorna informacija (telefonija) ili telegrafija, odnosno audio frekvencijski opseg 300 Hz – 3 kHz, maksimalna devijacija praktično ne treba prelaziti ±5 kHz. Uz najveći dopušteni indeks modulacije za NFM veze M=1, ukupna širina kanala koju će zauzeti NFM modulacija je 12 kHz.

Iz svega proizlazi da bi mi frekvenciju oscilatora od 5 MHz trebali mijenjati za oko 2 kHz kako bi na 5. harmoniku imali devijaciju od ±5 kHz. Prema našim testovima ovo bi trebalo biti izvedivo. Druga mogućnost je upotrijebiti kristal na 2,5 MHz i koristiti 10. harmonik. Tada bi bila dovoljna promjena frekvencije od oko 1 kHz. Ovo je vjerojatno bolja opcija jer će kristal biti manje opterećen, a oscilator će se lakše modulirati i svakako će biti stabilniji.

Kako god bilo, sada moramo izvesti neke praktične krugove oscilatora i testirati moguće FM devijacije sa istima.

Koje specifikacije FM modulacije moramo postići: devijacija, indeks modulacije, zauzeće frekvencijskog kanala

Što se tiče frekvencijske modulacije važno je znati nekoliko praktičnih stvari i razlika s obzirom na amplitudnu modulaciju. Kod amplitudne modulacije je širina zauzeća kanala (frekvencijskog opsega) otprilike jednaka dvostrukoj vrijednosti najviše modulacijske frekvencije. To znači da ako audio-frekvencijskim opsegom 300-3000 Hz amplitudno moduliramo neku noseću frekvenciju, onda će puni AM signal zauzeti opseg od 6 kHz (2 x 3 kHz). Međutim, ako istim audio opsegom frekvencijski moduliramo neku noseću frekvenciju, onda će FM signal zauzeti višestruko širi frekvencijski opseg, teoretski će se harmonici osnovne modulirane frekvencije protezati u beskonačnost kroz čitav RF opseg. U praksi je naravno svaki viši harmonik manje snage, te se za širinu opsega računaju samo harmonici kojima je amplituda viša od 10 % amplitude nemoduliranog (punog) vala nosioca. Naime, kod FM modulacije val nosilac nije konstantne amplitude nego se više ili manje smanjuje s obzirom na modulacijsku frekvenciju, a isto vrijedi i za bočne harmonike kao produkte modulacije.

Nama je važno zadržati širinu frekvencijske modulacije u određenom kanalnom opsegu kako signal jednog kanala ne bi prelazio i miješao se sa signalima susjednog kanala. Uobičajene širine kanala u NFM radio vezama su 12,5 i 25 kHz. Većina FM prijemnika stoga ima podešene MF filtre na prijem tih širina opsega. To znači da će prijemnik ionako filtrirati širi frekvencijski opseg, no kod FM modulacije to može onda značiti i degradaciju (izobličenje) demodulirane govorne informacije. Stoga naš modulator nikako ne bi smio generirati širi frekvencijski opseg. Širina opsega kao i kod AM modulacije ovisi dijelom od maksimalne audio frekvencije kojom moduliramo noseću frekvenciju, no jednako tako širina zauzeća kanala će kod FM ovisiti i o indeksu modulacije.

Indeks modulacije je omjer između devijacije (frekvencijskog pomaka noseće frekvencije) i najveće modulacijske (audio) frekvencije. Kod NFM govornih komunikacija taj indeks je 1 ili 2. Najveću modulacijsku frekvenciju ćemo ograničiti na standardnih 3 kHz koliko je dovoljno za razumljiv prijenos govora. Time na širinu kanala možemo još jedino utjecati devijacijom. Što je devijacija veća, to će širina zauzeća kanala biti veća ali će i glasnoća demoduliranog zvuka u prijemniku biti veća. Ako je devijacija premala, zvuk u prijemniku će biti jedva čujan i na maksimalnoj glasnoći. Treba je dakle naći devijaciju gdje se dobiva najbolji omjer između zauzeća kanala i čujnosti signala na prijemniku.

Uz modulacijski indeks 1 (M=1) i najveću modulacijsku frekvenciju od 3 kHz širina zauzeća kanala će biti 12 kHz. To je osnovna postavka standardnog NFM radio kanala. To također znači da na našem oscilatoru 25 MHz moramo postići devijaciju frekvencije od 3 kHz. S obzirom da koristimo 5. harmonik, onda devijacija kristalnog oscilatora na 5 MHz mora biti 600 Hz. Na osnovu naših prijašnjih mjerenja ovo možemo postići i na serijskoj i na paralelnoj rezonanciji kristala. Bez obzira na to, naručio sam i kristale za 2,5 MHz jer će onda potrebna devijacija biti dvostruko manja, što bi se u praksi moglo pokazati boljim.

Prvi testni modulirani kristalni oscilator

Prve testove Colpitts i Pierce kristalnih oscilatora radili smo na eksperimentalnoj ploči. To svakako nije najbolji način praktičnog testiranja sklopova koji rade na visokim frekvencijama, no u ovoj fazi samo želimo vidjeti koliko su ovi oscilatori pogodni za FM modulaciju.

Testni sklop smo napravili tako da možemo mijenjati prednapon baze i kolektorsku struju tranzistora, te naravno vanjske kapacitete serijski i paralelno vezane kristalu. Upotrijebljen je tranzistor 2N3904 i napajanje od 5 V. Kao promjenjivi kapacitet za modulaciju koristimo VHF kapacitivnu diodu BB 910 koja prilično linearno mijenja kapacitet u rasponu 2,3 do 38 pF ovisno o primijenjenom naponu u rasponu 28 – 0,5 V (što je napon viši to je kapacitet niži). Po potrebi ćemo paralelno spojiti dvije ili tri takve diode kako bi se ukupni kapacitet povećao.

Colpitts kristalni oscilator

Prvo smo testirali osnovnu shemu za tranzistorski Colpitts oscilator. S obzirom da je pojačalu u spoju emiterskog slijedila, najveća izlazna amplituda signala koju smo mogli dobiti je oko 0,6 Vpp. Oscilator će biti stabilniji i harmonički čišći što se manje opterećuje (manja povratna sprega) tako da najbolje radi kada izlazna amplituda ne prelazi 0,2 Vpp. Ako se oscilator preuzbudi onda dolazi do velikog izobličenja i nestabilnosti oscilacija tako da tranzistor lako može prestati oscilirati ili ući u svoje nekontrolirane VF samooscilacije. Za naše potrebe pak je potreban signal jačine barem 1 Vpp tako da obavezno moramo dodati barem jedan stupanj pojačanja.

Što se tiče harmonika, izlaz iz oscilatora može biti harmonički prilično čist što svakako ne odgovara našim potrebama. Određenim podešavanjima možemo dobiti jače harmoničke frekvencije, no one neće biti ni blizu jačine kao kod pravokutnih oscilatora. To svakako nije povoljno za naše potrebe.

Spektralni prikaz izlaznog signala iz Colpitts oscilatora. Donekle su izražena samo prva dva harmonika koja su -40 dB i -50 dB potisnuta ispod razine osnovnog signala.

Spektralni prikaz izlaznog signala iz Colpitts oscilatora. Donekle su izražena samo prva dva harmonika koja su -40 dB i -50 dB potisnuta ispod razine osnovnog signala.

Ovo je podešenje našeg Colpitts oscilatora tako da se dobiju najjači harmonici. Nama zanimljivi 5. harmonik je gotovo 36 dB slabiji od osnovnog signala.

Ovo je podešenje našeg Colpitts oscilatora tako da se dobiju najjači harmonici. Nama zanimljivi 5. harmonik je gotovo 36 dB slabiji od osnovnog signala.

Testom smo utvrdili da Colpitts oscilatorom možemo dobiti 5. harmonik na 25 MHz razine svega -45 dB. Čak i ako izuzmemo gušenje uslijed eksperimentalne montaže i povećano napon napajanja, i dalje ćemo trebati pojačalo od barem 40 dB da dobijemo dovoljno jak signal za naše potrebe (oko 5 dB). To su barem dva stupnja tranzistorskog pojačanja.

Test frekvencijske modulacije je pokazao da se ona može postići i na prijemniku se hvata demodulirani signal čak i na nekoliko centimetara udaljenosti od oscilatora. Međutim, ugađanje optimalne devijacije je posve druga priča. U osnovnom sklopu možemo samo kombinirati jačinu modulacijskog signala i broj upotrijebljenih kapacitivnih dioda da se dobije optimalna devijacija oscilatora. Svakako ne bi bilo loše izvesti kontrolu prednapona za kapacitivne diode kako je prikazano na drugoj i trećoj shemi. Tako se može podesiti raspon promjene kapaciteta u odnosu na raspon promjena amplitude modulirajućeg signala čime se onda može i finije podesiti ne samo željena devijacija nego i linearnost FM modulacije.

U trećoj shemi je za liniju prednapona kapacitivnih dioda dodana stabilizacijska zener dioda tako da prednapon nije ovisan o promjeni napona napajanja. Nadalje, jedan od problema je postići dobro odvajanje modulacijskog NF signala od VF signala oscilatora. Tu mogu pomoći niskopropusni i visokopropusni filtri koje je naravno potrebno dobro proračunati i praktično izvesti da bi bili funkcionalni. Kod RF tunera i sličnih oscilatorskih krugova kontroliranih kapacitivnim diodama često vidimo kombinaciju dvije kapacitivne diode zajedno vezane katodama ili anodama. Iako se ovim krugom dvostruko smanjuje efektivni kapacitet koji ima jedna dioda, s druge strane se postiže dobro odvajanje upravljačkog napona od oscilatorskog kruga. Ulazni upravljački audio signal se u startu uvodi kroz niskopropusni LC filtar koji će bez gušenja propuštati DC i NF audio napon i sprječavati prodor VF napona iz oscilatora na audio krugove. Zavojnica vezana u seriju sa kristalom omogućuje njegovo fino podešavanje na centralnu noseću frekvenciju. Također, na izlazu iz oscilatora imamo podešen LC krug kojim se filtrira željeni harmonik.

Shema na trećoj slici je stoga neki minimum sklopova koji bi morali imati za postizanje dobre FM modulacije kristalnog oscilatora na njegovom 5. harmoniku. Ovo svakako nije sklop koji se može testirati na eksperimentalnoj ploči. Treba je napraviti teoretski proračun, a zatim sklop izvesti na pravoj pločici slijedeći sva pravila za izradu VF sklopova.

Ukupno gledano, za Colpitts oscilator moramo ugraditi dvostupanjsko RF pojačalo i dodati LC ili RC filtre za dobro odvajanje DC i NF modulirajućeg napona od VF napona koji generira oscilator. Tu je naravno obavezan i pojasni filtar za 5. harmonik. Zapravo, vrlo slabi harmonici koje generira ovaj oscilator najveći su nedostatak da ga odaberemo za našu primjenu.

Pierce kristalni oscilator

Kod Pierce oscilatora napon uzimamo sa kolektora tranzistora tako da je on veće amplitude od onoga sa Colpitts oscilatora. Izlazni signal može biti slične čistoće kao i kod Colpitts oscilatora, no moguće je napraviti ugađanje tako da je 5. harmonik 25 dB slabiji od osnovnog signala. To je puno bolje od Colpitts oscilatora, no i dalje trebamo jedan ili dva stupnja RF pojačanja (najbolje jedan stupanj za odvajanje i jedan stupanj RF pojačanja).

Sve drugo vrijedi kao i za Colpitts oscilator. Osnovna FM modulacija se postiže jednostavnom shemom, no za bolju čistoću, kontrolu i podešavanje modulacije treba dodati sklopove koji uključuju podesive filtre, zavojnice i slične elemente koje želimo izbjeći.

Najjači harmonici koje smo uspjeli dobiti podešenjem Pierce oscilatora. Ovdje se nešto veće razine harmonika postižu najviše iz razloga jer je i osnovni signal jači nego kod Colpitts oscilatora. Povećanjem napona napajanja sa 5 V na 12 V bi se vjerojatno dobio dovoljno snažan 5. harmonik, no i dalje moramo ugraditi barem jedan tranzistorski stupanj za odvajanje.

Najjači harmonici koje smo uspjeli dobiti podešenjem Pierce oscilatora. Ovdje se nešto veće razine harmonika postižu najviše iz razloga jer je i osnovni signal jači nego kod Colpitts oscilatora. Povećanjem napona napajanja sa 5 V na 12 V bi se vjerojatno dobio dovoljno snažan 5. harmonik, no i dalje moramo ugraditi barem jedan tranzistorski stupanj za odvajanje.

Generalni zaključak je da tranzistorski kristalni oscilatori nisu najbolje rješenje za naše potrebe, posebice ne ako se baziraju na jednom tranzistoru. Da bi dobili zadovoljavajuće dobar modulator shema se prilično komplicira i potrebno je puno eksperimenata (podešavanja) koje nije lako praktično izvesti. Sve to možda i nije problem ako želimo napraviti jedan modulator za specifičnu primjenu, no nama je osnovni zahtjev izvesti jednostavan i jeftin sklop koji se lako i brzo izrađuje u više primjeraka, tako da od jednostavnih tranzistorskih modulatora odustajemo, jednako kao što smo od njih morali odustati i kod amplitudne modulacije. Sa jednim tranzistorom se jednostavno ne može postići dovoljna kvaliteta modulacije.

Druge opcije

Na tržištu postoje gotovi integrirani krugovi koji sadrže kvalitetne VCO ili PLL/VCO sklopove, no za 25 MHz je ponuda zapravo vrlo ograničena i takvi čipovi/moduli nisu baš jeftini. Generalno se teško takav sklop može kupiti ili napraviti za cijenu ispod 50 eura.

Istraživao sam i ponudu različitih jeftinih gotovih FM modula predajnika kontroliranih PLL-om za komercijalni UKV FM radio opseg, koji se prodaju kao bežični mikrofoni, bežični audio svirači za automobilske radio prijemnike i slično. Međutim, svi takvi FM predajnici se baziraju na namjenskim čipovima za opseg 75-110 MHz te za niti jedan nema potvrde da radi ispod 70 MHz. Preskaleri, digitalni djelitelji ili mješači koji bi se mogli upotrijebiti za snižavanje frekvencije (npr. 100 MHz na 25 MHz) su također rijetki ili preskupi.

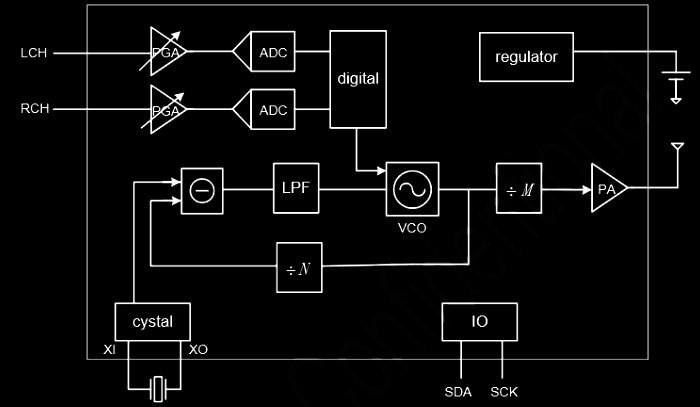

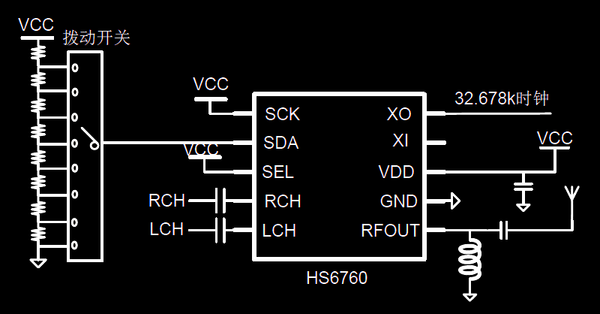

Najbliža mogućnost našim zahtjevima je kineski čip oznake HS6760. To je kompletni stereo FM predajnik za frekvencijski opseg 27-125 MHz. Može se modulirati izravno audio signalom iz mikrofona ili linijskim audio signalom max. 600 mVpp. Izlazna RF snaga je podesiva u 30 koraka u rasponu od -6 dB do 24 dB. Podržan je standardni 75 µs pre-emphasis, te tri nivoa devijacije: 75 kHz, 50 kHz i 22,5kHz. Radi na naponu napajanja 3,3 V (2,2-4,2 V). Programira se preko standardne I2C sabirnice. Može se programirati do 8 frekvencija, a one se onda mogu na jednom programiranom modulu mijenjati bez potrebe za bilo kakvim dodatnim hardverom, preko jednostavnog otporničkog djelitelja napona.

Ovo je doista sve što nam treba. Međutim, problem je što se na Internetu mogu naći samo šturi tvornički podaci o načinu programiranja ovog čipa (u programskom jeziku C) i to isključivo na kineskom jeziku. Treba biti iskusan programer za I2C podatkovne sabirnice kako bi se ovaj čip ispravno programirao ili kako bi se neke njegove funkcije (poput promjene FM devijacije) mogle izvesti na vanjske kontrole (za što je onda svakako potreban dodatni MCU). Nisam pronašao nikakve projekte ni forumske rasprave vezane uz ovaj čip. Ukoliko ne nađem drugo rješenje, morat ću se sam upustiti u programiranje ovog čipa, što naravno u slučaju neke greške vrlo lako može dovesti do njegovog uništenja.

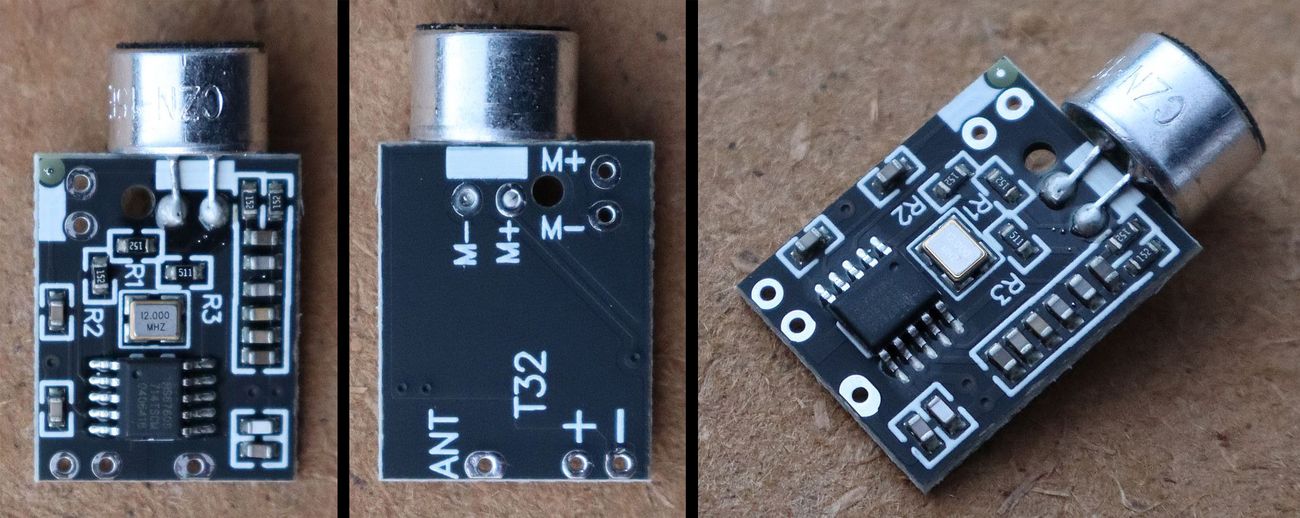

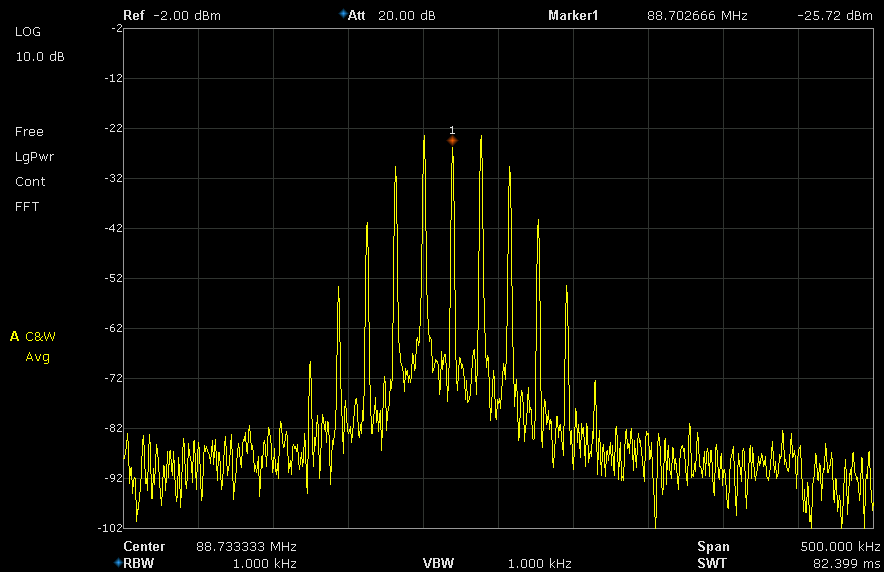

Čip HS6760 dolazi u minijaturnom SSOP-10 kućištu, a ovdje je gotov modul programiranog stereo FM predajnika na 6 radijskih FM frekvencija (inicijalna frekvencija je 88,7 MHz). Modul košta cca 7 eura.

Čip HS6760 dolazi u minijaturnom SSOP-10 kućištu, a ovdje je gotov modul programiranog stereo FM predajnika na 6 radijskih FM frekvencija (inicijalna frekvencija je 88,7 MHz). Modul košta cca 7 eura.

I na primjeru čipa HS6760 jasno se vidi koliko je digitalna elektronika, odnosno digitalno procesuiranje signala postalo superiornije nad analognom obradom signala. Što se tiče elektronike, lemilicu je potrebno polako zamjenjivati mišem i tipkovnicom, ukoliko se želi ići u korak s vremenom.

Mi ćemo ipak u posljednjem pokušaju dati šanse još jednoj „neprogramiranoj“ mogućnosti izrade dovoljno dobrog i jeftinog kristalnog FM modulatora. Stoga se prebacujemo opet na relaksacijske oscilatore bogate harmonicima i to opet uz upotrebu jeftinih logičkih integriranih krugova.

Kristalni oscilator sa inverterom (NOT logička vrata)

Kada smo eksperimentirali sa FM modulatorom baziranom na čipu SN74LS13 spomenuli smo da se interna građa logičkih krugova uglavnom bazira na serijskim i paralelnim kombinacijama P-MOS i N-MOS tranzistora. Evo osnovne interne sheme jednog CMOS logičkog invertera ili NOT logičkih vrata.

CMOS inverter se sastoji od spoja P-MOS i N-MOS tranzistora tako da invertiraju (okreću) ulazni napon. Kada je ulazni napon nizak (logička nula) onda je P-MOS uključen, a N-MOS isključen te je na izlaz proslijeđen napon napajanja, odnosno visoka naponska razina ili logička jedinica. Isto tako, kada je ulazni napon visok (logička jedinica) onda je N-MOS uključen, a P-MOS isključen što rezultira izlazom na razini mase, odnosno niska naponska razina ili logička nula.

Prebacivanje između dva logička stanja je ukupno gledano nelinearno, odnosno gotovo skokovito. Do određene razine ulaznog napona N-MOS tranzistor neće voditi, a onda će na određenom pragu okidanja naglo provesti. Vrijedi naravno i obrnuto za pad ulaznog napona i P-MOS tranzistor.

Ono pak što je nama zanimljivo, to je da postoji neko područje napona u sredini (između dva praga okidanja) gdje se događa to brzo prebacivanje s jednog stanja u drugo. Koliko god to prebacivanje bilo brzo sa velikom strminom promjene stanja, ipak je potrebno neko vrijeme da se isto dogodi. Štoviše, to područje brzog porasta napona ili brzog pada napona je gotovo linearno, te to usko područje možemo promatrati kao područje linearnog rada tranzistora.

Ukoliko dakle tranzistore u inverteru želimo koristiti kao linearna pojačala (tako da rade samo u uskom linearnom području), to možemo napraviti pravilnim prednaponom (konstantnim istosmjernim naponom ili biasom) na gate-ovima tranzistora. Srećom, to je praktično vrlo jednostavno izvesti. Potrebno je samo između izlaza i ulaza invertera napraviti povratnu vezu sa otpornikom dovoljno velike vrijednosti (više od 500 kΩ, tipično 1-1,5 MΩ). Time se inverter pretvara u „self-biased“ linearno pojačalo.

Naravno, da bi pojačalo radilo linearno ulazni signal mora biti ograničene amplitude kako bi ostao unutar linearnog područja rada tranzistora. Također, napon napajanja te ulazna i izlazna impedancija imaju utjecaj na veličinu i frekvencijski opseg pojačanja. Inverteri se inače vrlo često koriste kao „self-biased“ linearna pojačala za različite namjene, posebno za kristalne oscilatore takta.

Kristalni oscilator sa inverterom u spoju pojačala koji radi na serijskoj rezonanciji kristala (lijevo) i paralelnoj rezonanciji kristala (desno).

Kristalni oscilator sa inverterom u spoju pojačala koji radi na serijskoj rezonanciji kristala (lijevo) i paralelnoj rezonanciji kristala (desno).

Koji inverter odabrati

Postoji više inačica CMOS invertera u više različitih kućišta. Ono na što bi se trebalo paziti (prema nekim forumima) to je da se uzimaju „čisti“ inverteri, dakle oni koji nisu opremljeni dodatnim buferima (pojačalima za odvajanje). Oznake takvih čistih CMOS invertera obično sadrže slovo „U“ u sufiksu (Unbuffered), poput CD4049UB, CD4069UB, 74HCU04. Neke 74xx serije čipova mogu imati samo slovo „C“ u sredini (74C04) što također radi, no primjerice 74HC04 nije iskoristiv za tu namjenu. Načelno se mogu koristiti inverteri sa Schmitt triggerima, no moraju imati oznake „U“ ili „C“ kako smo opisali. Svakako nisu za upotrebu TTL serije čipova poput 74LS04, 7404 ili 74S04. Osim invertera mogu se upotrijebiti i drugi čipovi koji sadrže komplementarne parove N-MOS i P-MOS tranzistora poput CD4007UB.

U zalihama smo pronašli jedan čip HEF4069UBP koji odgovara našim potrebama. Čip sadrži šest čistih invertera i može raditi na naponima napajanja 5-15 V. Evo kako se tih šest invertera može iskoristiti za naš projekt.

Prvi inverter je u spoju „self-biased“ pojačala kojem je pojačanje određeno otpornicima od 10 kΩ i 1 MΩ. Time ovaj inverter služi kao pojačalo modulirajućeg audio signala i ujedno kao izolator između NF audio signala i VF signala oscilatora. Drugi inverter je također u spoju „self-biased“ pojačala i radi kao oscilator na frekvenciji kristala od 5 MHz. Frekvencijska modulacija se vrši preko dvije paralelno spojene kapacitivne diode BB 910 serijski vezane ulaznom „load“ kondenzatoru kristala. Time se djeluje na njegovu paralelnu rezonantnu frekvenciju. Treći inverter je pojačalo za odvajanje (bufer), a preostala tri invertera su spojena paralelno u cilju strujnog pojačanja, odnosno kako bi na izlazu moglo biti veće opterećenje.

S obzirom da koristimo 5. harmonik, kako bi oscilator dobro radio za takt modula Si5351A, ovdje moramo filtrirati sve druge harmonike većih amplituda, posebice osnovnu frekvenciju i više harmonike. Najlakše je bilo upotrijebiti gotove keramičke filtre (rezonatore) za 25 MHz. Frekvencijska propusnost keramičkih rezonatora (za razliku od kristalnih) je puno šira tako da bez problema prolazi puna devijacija frekvencije. Za keramičke filtre (pojasno-propusne filtre) je važno prilagoditi ulaznu i izlaznu impedanciju kako bi dobro radili. Mi na eksperimentalnoj ploči nismo podešavali te krugove, nego smo serijski povezali tri keramička rezonatora čime su svi harmonici potpuno potisnuti tako da na 25 MHz dobivamo čisti sinusni signal.

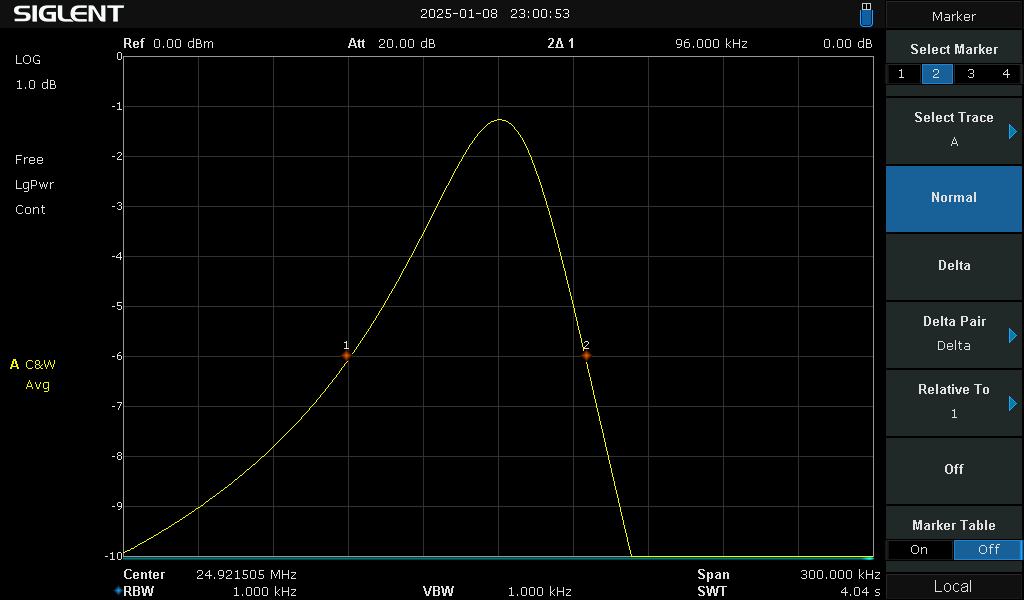

Na snimku frekvencijsko-amplitudne karakteristike keramičkog filtra 25 MHz vidi se da je propusnost gotovo 100 kHz (6 dB) što je više nego dovoljna propusnost za FM modulaciju.

Na snimku frekvencijsko-amplitudne karakteristike keramičkog filtra 25 MHz vidi se da je propusnost gotovo 100 kHz (6 dB) što je više nego dovoljna propusnost za FM modulaciju.

Test je pokazao da ovakav FM oscilator radi vrlo dobro, čak i na eksperimentalnoj ploči. Na 5. harmoniku se bez problema postiže modulacija za zauzećem pojasa ne većim od 25 kHz. Demodulirani signal na prijemniku je vrlo čist i neizobličen. Ovo je svakako najbolji kandidat za našu primjenu.

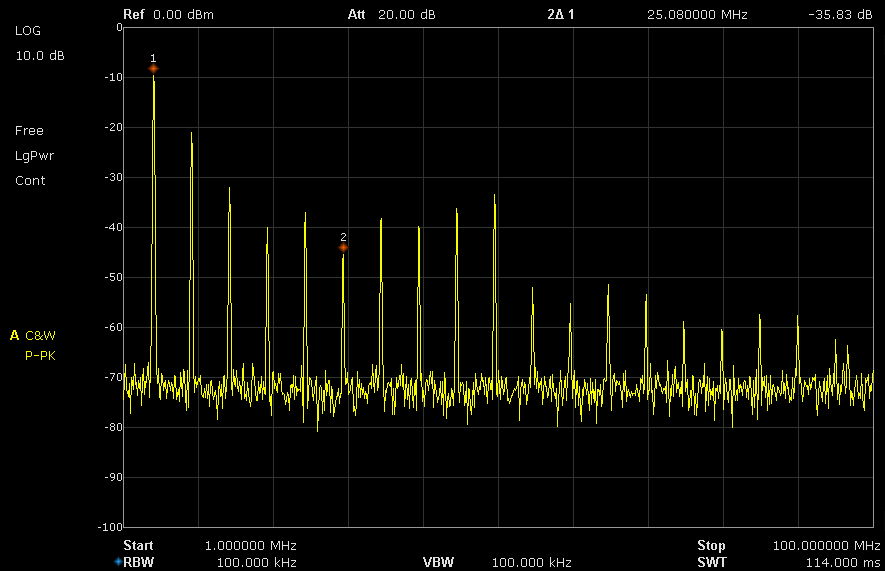

Harmonička slika izlaza iz oscilatora bez filtriranja. Vidi se da je 5. harmonik 15 dB slabiji od osnovnog signala na 5 MHz i iznosi -8 dBm. To je daleko jači signal od onih koje smo mogli dobiti tranzistorskim Colpitts i Pierce oscilatorima.

Harmonička slika izlaza iz oscilatora bez filtriranja. Vidi se da je 5. harmonik 15 dB slabiji od osnovnog signala na 5 MHz i iznosi -8 dBm. To je daleko jači signal od onih koje smo mogli dobiti tranzistorskim Colpitts i Pierce oscilatorima.

FM modulacija 5. harmonika na 25 MHz audio signalom raspona 300 Hz – 3 kHz. Jedna podjela je 5 kHz. Vidi se kako signal ne zauzima širinu veću od 25 kHz.

FM modulacija 5. harmonika na 25 MHz audio signalom raspona 300 Hz – 3 kHz. Jedna podjela je 5 kHz. Vidi se kako signal ne zauzima širinu veću od 25 kHz.

Gotov predajnik sa HS6760

Iako bi oscilator sa inverterom mogao biti dobar kandidat za naše potrebe (dobro radi i jednostavan je za praktičnu gradnju), teško je odoljeti gotovom digitalnom rješenju u obliku čipa HS6760 koji smo prethodno spomenuli. Svakako želimo napraviti barem osnovne testove ovog FM modulatora, a ako se pokaže da radi puno bolje od kristalnog oscilatora sa inverterom, onda ćemo se potruditi programirati ga na 27 MHz.

Modul FM predajnika sa HS6760 kakav za cca 7 eura možete naručiti iz Kine, prema opisu je tvornički programiran i podešen za stereo WFM odašiljanje na fiksnoj frekvenciji od 88,7 MHz. Izmjenom otpornika R1 i R2 u djelitelju napona za pin 2 (SDA) može se odabrati neka druga od šest pred-programiranih frekvencija. Napajanje mora biti u granicama 2,2 V do 4,2 V tako da je najbolje koristiti standardnih 3,3 V.

Dva stereo audio ulaza su na modulu pripremljena za spajanje kondenzatorskih electret mikrofona, odnosno na obje ulazne audio linije je doveden napon za napajanje mikrofona, s time da je na jednoj liniji već zalemljen mikrofon. To znači da ako dovodimo neke linijske audio ulaze oni moraju ići preko kondenzatora za DC odvajanje. Modul je podešen za stereo emitiranje (pin 1-SCK vezan na Vcc). Primarno je namijenjen za bežično odašiljanje vanjskih zvukova uhvaćenih preko mikrofona, odnosno kao neki baby-alarm, bežični mikrofon, električni pickup za klasične muzičke instrumente i slično.

Elektronička shema modula FM predajnika sa HS6760 i vrijednosti otpornika R1 i R2 za odabir jedne od šest pred-programiranih frekvencija.

Elektronička shema modula FM predajnika sa HS6760 i vrijednosti otpornika R1 i R2 za odabir jedne od šest pred-programiranih frekvencija.

Interna blok shema čipa HS6760.

Interna blok shema čipa HS6760.

Mjerenje frekvencijske širine izlaznog RF signala iz čipa HS6760

Prvi test ovog modula je pokazao da je prijenos zvuka na razini kvalitete komercijalnih FM radio postaja. Napravili smo usporedne snimke zauzeća frekvencijskog kanala s obzirom na amplitudu i frekvenciju modulirajućeg signala. Već smo rekli da zauzeće FM opsega ne ovisi samo o maksimalnoj frekvenciji koja se modulira, nego i o amplitudi (jačini) modulirajućeg signala.

Što se tiče amplitude, našli smo da je razina audio signala od 5 mVpp minimalna za postizanje dovoljne glasnoće na prosječnom prijemniku. Isto tako, sa razinom audio signala od 40 mVpp se već dobiva vrlo glasna demodulaciju na prijemniku. Stoga smo napravili testove na ove dvije razine amplituda.

Što se tiče frekvencijskog opsega, za kvalitetan WFM prijenos muzike potrebno je prenijeti frekvencijski opseg 20 Hz – 16 kHz. Za govornu NFM modulaciju pak je dovoljno prenijeti audio opseg raspona 300 Hz – 3 kHz. Stoga smo testove napravili i na ova dva opsega.

Ovdje su snimci zauzeća frekvencijskog opsega za MONO odašiljanje (kod mono odašiljanja aktivan je samo lijevi kanal, pin 5 – LCH). Lijepo se može vidjeti kako zauzeće kanala puno više ovisi o amplitudi, nego o frekvenciji modulirajućeg signala.

Ovdje su snimci zauzeća frekvencijskog opsega za MONO odašiljanje (kod mono odašiljanja aktivan je samo lijevi kanal, pin 5 – LCH). Lijepo se može vidjeti kako zauzeće kanala puno više ovisi o amplitudi, nego o frekvenciji modulirajućeg signala.

Ovdje su snimci zauzeća frekvencijskog opsega za STEREO odašiljanje (isti signal je doveden na oba stereo ulaza). Lijepo se može vidjeti kako zauzeće kanala puno više ovisi o amplitudi nego o frekvenciji modulirajućeg signala.

Ovdje su snimci zauzeća frekvencijskog opsega za STEREO odašiljanje (isti signal je doveden na oba stereo ulaza). Lijepo se može vidjeti kako zauzeće kanala puno više ovisi o amplitudi nego o frekvenciji modulirajućeg signala.

Na stereo načinu rada, čak i kad nema nikakve audio modulacije (oba audio ulaza spojena na masu) stalno je prisutna modulacija stereo pilot-tonom od 19 kHz.

Na stereo načinu rada, čak i kad nema nikakve audio modulacije (oba audio ulaza spojena na masu) stalno je prisutna modulacija stereo pilot-tonom od 19 kHz.

Ostale mogućnosti čipa HS6760

Na našem modulu je predviđena jedino promjena šest pred-programiranih radnih frekvencija u uskom opsegu 76-88,7 MHz i to promjenom vrijednosti dva otpornika na pločici. Odmah ćemo reći da je čip tvornički zapravo programiran na osam frekvencija (87,5 MHz / 88,1 MHz / 88,3 MHz / 88,5 MHz / 88,7 MHz / 40,0 MHz / 64,0 MHz / 76,0 MHz), no u podacima se ne navode one izvan komercijalnog UKV FM opsega. Ako se pin 2 spoji preko potenciometra (10 kΩ) na Vcc i GND jednostavno i lako ćete mijenjati svih osam frekvencija.

Osim toga, moguće je napraviti jednostavnu modifikaciju na pinu 1, tako da možemo birati između STEREO i MONO odašiljanja. Ako je pin 1 spojen na Vcc (pozitivni pol napajanja) odašiljanje će biti STEREO, a ako je spojen na GND (masa, minus pol napajanja) odašiljanje će biti MONO.

Za sve ostalo moramo vršiti programiranje čipa, a mogućnosti za to su široke:

- programiranje do osam frekvencija u rasponu 27-125 MHz (korak 50 kHz)

- programiranje frekvencijske devijacije u tri koraka: 75kHz, 50kHz i 22,5kHz

- kontroliranje načina rada čipa: Normal, Mute, Standby, Sleep

- mogućnost rada sa četiri različita kristala: 24 MHz, 12 MHz, 7,6 MHz, 32,768 kHz i odabir načina dijeljenja frekvencije takta

- programiranje pre-emphasisa od 50 µs ili 75 µs, te podešavanje njegovog pojačanja

- programiranje pojačanja audio pojačala u rasponu -6 dB do 24 dB u 8 koraka

- programiranje izlazne RF snage u rasponu -15 dBm do 10 dBm u 30 koraka

- programiranje FM devijacije: 75 kHz, 50 kHz ili 22,5 kHz

- Automatska MUTE funkcija za audio signal sa podešavanjem pragova okidanja i vremena reakcije

- Automatska kontrola pojačanja sa podesivim pragovima reakcije

- Automatsko isključivanje audio i/ili RF pojačala kada nema ulaznog audio signala

- definiranje najniže audio frekvencije koja prelazi DC prag: 14 Hz, 28 Hz, 56 Hz, 112 Hz

- kalibracija izlaznog RF pojačala

Dostupni podaci za čip HS6760

Čip HS6760 se od početne inačice v1.0 s kraja 2015. godine postepeno razvijao tako da, prema podacima koje sam uspio naći, posljednja šesta inačica ovog čipa ima oznaku v2.4 i datira iz srpnja 2016. godine. Našao sam osnovne tvorničke podatke za inačice v1.3, v2.0 i v2.4 (datasheetna kineskom jeziku) iz kojih se mogu iščitati opće značajke i način programiranja čipa preko I2C sabirnice. Za inačicu v1.3 je dat i osnovni program u C programskom jeziku za programiranje radnih parametara čipa.

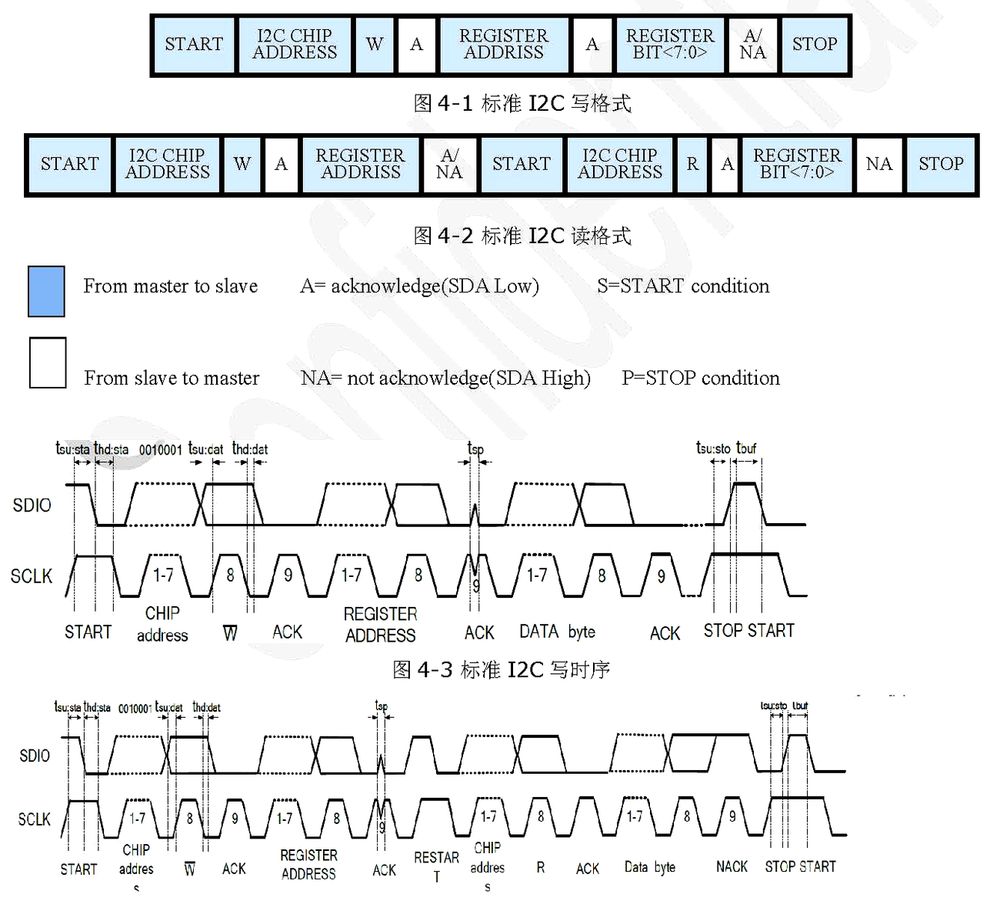

Programiranje preko I2C protokola

Već smo rekli da se programiranje čipa HS6760 vrši preko široko korištene standardne serijske I2C sabirnice za koju su dovoljne dvije žice: SCK (takt signal) i SDA (dvosmjerna razmjena podataka). Da bi se čip prebacio u mod programiranja, pin 3-SEL se mora sa visoke logičke razine (Vcc) prebaciti na nisku logičku razinu (masa). Tada pinovi SCK i SDA više se služe za setiranje mono/stereo načina i odabir kanalne frekvencije, nego za I2C komunikaciju. Također, koliko sam uspio prevesti kineski datasheet, čini se da se čip automatski resetira na tvorničke postavke svaki put kada se pin 3-SEL spoji na masu.

I2C (Inter-Integrated Circuit)

I2C (Inter-Integrated Circuit) standard omogućuje komunikaciju između velikog broja digitalnih uređaja gdje su svi paralelno povezani preko samo dvije fizičke žice. Pošto se koristi serijska komunikacija onda je u jednom trenutku moguća razmjena podataka između samo između dva uređaja, a selektiranje željenog uređaja se vrši preko njegove jedinstvene programske adrese.

O I2C komunikaciji postoji puno internetskih tutorijala tako da ovdje neću prepisivati sve detalje i specifičnosti ovog protokola, želim se bazirati samo na one segmente koji su nužni za komunikaciju sa čipom HS6760.

Glavni uređaj u I2C komunikaciji koji istom upravlja u svim segmentima naziva se MASTER. Mi ćemo kao MASTER uređaj koristiti Arduino Mega 2560 mikrokontrolersku razvojnu ploču. SLAVE uređaj je naravno čip HS6760. On izvršava naredbe koje mu daje MASTER uređaj i šalje potvrdu da li su iste izvršene. Prvo moramo vidjeti koji je točan protokol slanja (zapisa) podataka na naš SLAVE čip, a to možemo vidjeti samo sa tvorničke dokumentacije čipa.

Ovo je u osnovi standardni protokol kod I2C komunikacije. Generalno gledano, prvo se inicira 7-bitna identifikacijska adresa uređaja (čip HS6760 kao SLAVE uređaj), a onda se razmjenjuju 8-bitni paketi podataka u određene registre čipa. Nakon svake identifikacije i svakog razmijenjenog paketa, mora se dobiti potvrdni bit da je paket uredno upisan ili pročitan. Potvrdni bit je označen slovom A (acknowledge), a ukoliko nema potvrde (neuspješna prijava na adresu ili neuspješna razmjena podataka) takav bit je označen sa NA ili NACK (not-acknowledge).

Organizacija podataka u registrima čipa HS6760

Nekako sam uspio prevesti kineske znakove do te mjere da mogu donekle shvatiti organizaciju podataka u registrima. Dokumentacija daje podatke samo o registrima u koje korisnik može upisivati bitove za definiranje rada čipa.

Tablica sa prikazom značenja pojedinih binarnih vrijednosti u registrima čipa HS6760 koji se mogu mijenjati.

Tablica sa prikazom značenja pojedinih binarnih vrijednosti u registrima čipa HS6760 koji se mogu mijenjati.

Usporedba definiranih tvorničkih vrijednosti registara čipa HS6760 prema datasheetu sa stvarnim pročitanim vrijednostima iz čipa. U crnim poljima su registri koji se mogu mijenjati (čitanje i pisanje), u sivim poljima su prazni (rezervirani) registri i registri u koje se ne mogu upisivati podaci.

Usporedba definiranih tvorničkih vrijednosti registara čipa HS6760 prema datasheetu sa stvarnim pročitanim vrijednostima iz čipa. U crnim poljima su registri koji se mogu mijenjati (čitanje i pisanje), u sivim poljima su prazni (rezervirani) registri i registri u koje se ne mogu upisivati podaci.

Rezultati čitanja registara pokazuju da su vrijednosti praktično identične tvorničkima (Factory Default), a razlika je samo u registru 0x02 što je i očekivano jer za gotov modul mora biti definiran upotrijebljeni kristal u našem slučaju od 12 MHz (tvornička je vrijednost 00). Također je razlika u dijelu zapisa koji se odnosi na postavke jačine izlaznog RF signala, koji je od tvornički definiranog minimuma (4/31 ili oko -12 dBm) povećan na 20/31 ili oko 10 dBm, što je razumljivo ako se čip koristiti kao bežični mikrofon bez dodatnih pojačala.

Specifično binarno kodiranje radnih frekvencija za upis u registre

Kao što se vidi iz naše tablice, kanalna frekvencija zauzima 8 bitova registra 0x00 i prvih 6 bitova registra 0x01. Pretvaranje frekvencije u binarni niz od 14 bitova je vrlo jednostavno. Željena frekvencija u MHz se pomnoži sa 20 čime se dobije određeni decimalni broj. Taj decimalni broj se zatim pretvori u heksadecimalni ili binarni broj koji se upisuje u registre. Osam nižih (zadnjih) bitova koji predstavljaju binarni broj frekvencije se zapisuje u registar 0x00, a preostalih šest viših bitova se zapisuju u registar 0x01.

Uzmimo na primjer da želimo upisati frekvenciju 90,5 MHz:

- 90,5 x 20 = 1810

- 1810 pretvoreno u heksadecimalni broj je 0x0712 (binarno 00000111 00010010)

- u registar 0x00 se upiše niži dio heksadecimalnog broja 0x12 (00010010)

- u registar 0x01 se upiše viši dio heksadecimalnog broja 0x07 (00000111)

- nakon što je frekvencija upisana, na najniži bit registra 0x02 (D0) treba upisati nulu, a zatim uz kašnjenje od 10 ms upisati jedinicu kako bi frekvencija bila setirana

Registri 0x00 i 0x01 za upis do najviše osam radnih frekvencija su privremeni. Kad se binarni kod za određenu frekvenciju unese u ove registre, setiranjem opisanim u 5. koraku ova frekvencija se prebacuje u drugi registar za njenu trajnu pohranu. Dokumentacija ne navodi koje su adrese tih trajnih memorijskih registara.

Hardversko povezivanje

Hardversko povezivanje čipa HS6760 sa nekom Arduino razvojnom pločom je vrlo jednostavno. Osim napajanja (3,3 V) potrebno je još samo povezati I2C sabirnicu, odnosno linije SCK i SDA. Kod Arduino Mega 2560 ploče, SCK linija je na D21, a SDA linija je na D20. Već smo rekli da nam pull-up otpornici nisu potrebni jer su isti ugrađeni u sam čip.

- VCC – 3V3 V

- GND – GND

- SDA (44 D20 Arduino Mega 2560) – SDA (pin 2 HS6760)

- SCK (43 D21 Arduino Mega 2560) – SCK (pin 1 HS6760)

Programiranje čipa HS6760 (Adruino IDE)

Jedini primjer programa za programiranje čipa HS6760 uspio sam izvući iz datasheeta za v1.3. Program je pisan u C jeziku. Ako nekoga zanima, originalni kineski datasheet sa primjerom programa može skinuti ovdje.

Inicijalni programski kod iz datasheeta je svakako treba dovršiti za pokretanje na određenoj platformi. Stoga sam ovaj kod prilagodio pokretanju na Arduino IDE platformi (uz veliku i svesrdnu pomoć ChatGPT-a :-).

Međutim, ni nakon sada već možda 50-tog pokušaja, čip HS6760 se ne želi pre-programirati i stalno ostaje na svojim tvorničkim postavkama:

- pokušao sam različite kombinacije programiranja frekvencije sa različito postavljenim set i reset funkcijama, slijedeći različite procedure, do sada ni jedna nije uspjela

- izvršio sam nekoliko testova I2C komunikacije sa čipom (čitanje i pisanje), sve prolaze

- smanjio sam brzinu komunikacije na minimalnu (100000) i ubacio kod za praćenje da li se podaci stvarno upisuju u registre – podaci se upisuju, sve radi po programu, ali čip na kraju i dalje ostaje na tvorničkim postavkama

Na kraju sam detaljno preveo posljednji kineski datasheet v2.4 koji je dostupan samo kao slika niske rezolucije originalnih PDF stranica, što je bio prilično naporan posao, no iz svega nisam saznao ništa novo. Inače, originalni PDF i originalni program za programiranje čipa su besplatni. Međutim, ni jedno ni drugo se ne može skinuti bez registracije na kineske stranice „gitcode.com“, registracija se ne može napraviti bez telefona (slanje SMS registracijskog koda), a taj kod nikako ne stiže na telefon koliko god puta ponovio zahtjev za istim.

Unatoč svim pokušajima i dalje problem može biti softverski, proceduralni ili hardverski. Svakim spajanjem pina-3 na masu čip se (prema upitno prevedenim uputama) resetira na tvorničke postavke, a onda može biti i problem u proceduri odspajanja čipa sa programatora. Kako god bilo, imam još desetke što softverskih, što hardverskih ideja za daljnje pokušaje (povećanje napona napajanja čipa sa 3,3 V na 4 V, upotreba ESP32 platforme umjesto Mega 2560, daljnje izmjene programskog koda…).

Analiza I2C signala na osciloskopu

S obzirom da sam probao na desetke programskih kodova i niti jedan nije uspio pomaknuti čip sa tvorničkih postavki, sada je najizgledniji problem u samom I2C komunikacijskom linku. Stoga idemo analizirati I2C signale na osciloskopu.

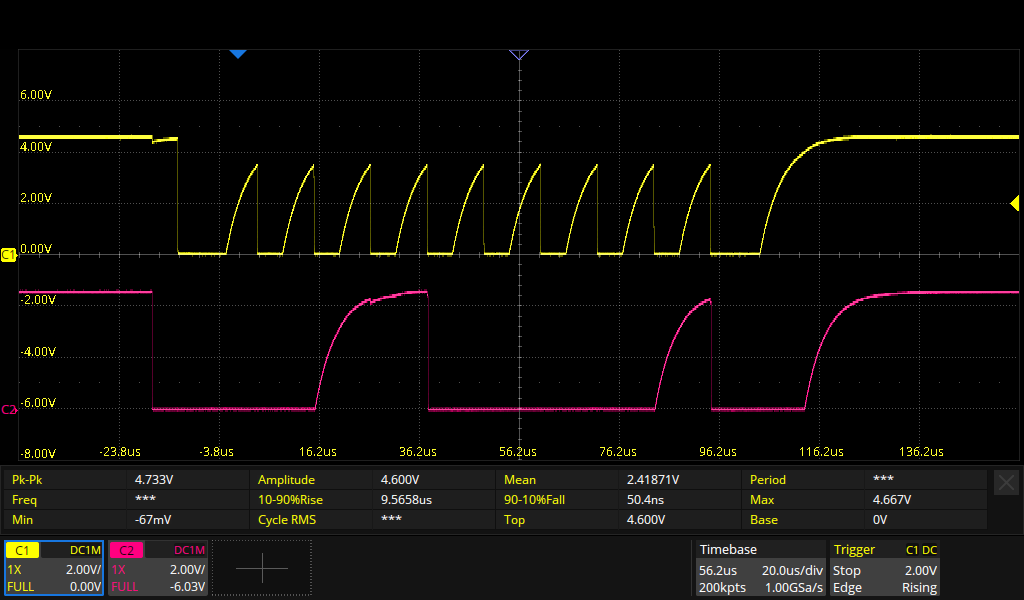

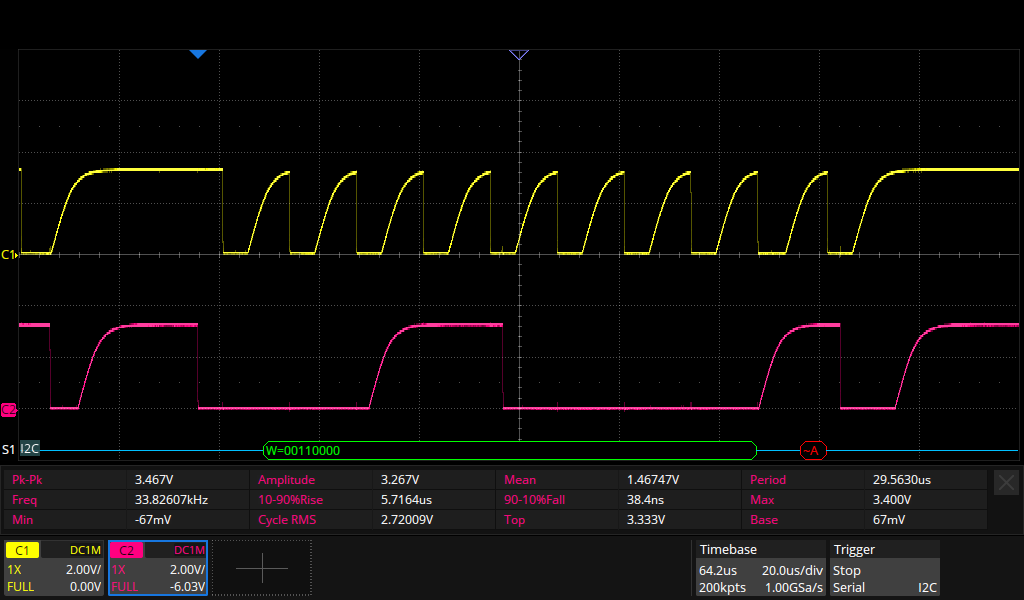

Izravni I2C signal sa Mega 2560 ploče je više nalik pilastom nego pravokutnom valnom obliku.

Izravni I2C signal sa Mega 2560 ploče je više nalik pilastom nego pravokutnom valnom obliku.

Ovo je I2C signal sa ploče Mega 2560, izravno sa pinova SCA i SDL. Negdje sam pročitao da ploča ima ugrađene pull-up otpornike od 10 kΩ. To su otpornici koji zatvaraju strujni krug izlaznih tranzistora za SCA i SDL linije sa pozitivnim polom napajanja, odnosno dovode pozitivni napon na kolektore tranzistora (unutar samog čipa su ovi tranzistori sa otvorenim kolektorom). Snimljeni signal jasno pokazuje da napon na tranzistorima stalno postoji jer je su stalno prisutne visoke naponske razine na oba pina (cca 4,7 V). Pojavom signala te linije se zapravo spajaju na masu pa je naponska razina nula. To znači da su interni pull-up otpornici stvarno ugrađeni.

Međutim, ne može se ne primijetiti kako je oblik signala daleko od pravokutnog, odnosno vrijeme porasta signala sa nule na jedinicu je vrlo dugačko što oblik signala čini više pilastim nego pravokutnim. To je normalno jer spajanje Vcc na GND (kratki spoj napona) se dogodi relativno brzo, no onda je za oporavak, odnosno vraćanje napona ponovno na maksimum treba neko duže vrijeme.

To vrijeme porasta signala ovisi o vrijednosti ugrađenog pull-up otpornika, ali i o parazitskim kapacitetima samih žica preko kojih se prenose I2C signali. Kod nas taj kapacitet sigurno nije problem jer žice nisu duže od 10 cm. Međutim, ni sam oblik signala ne bi trebao biti problem. Unatoč izraženoj kosini, još uvijek se jasno može odvojiti logička naponska razina za nulu i jedinicu kod svake promjene tih stanja.

Kako utječe nepravilan oblik signala na I2C komunikaciju

Generalno gledano, oblik signala sa naše slike koji je pilastog oblika, kao i onaj čistog pravokutnog oblika, jednako će dobro prenijeti I2C komunikaciju. Razlog tome je što svaki impuls uspijeva dostići svoj maksimum (puni Vcc) te će biti prepoznat kao logička jedinica, bez obzira što impuls nije posve pravokutan.

Međutim, signal sa velikim bočnim nagibima svakako utječe na maksimalnu brzinu koju možemo postići digitalnom komunikacijom. Pri velikim brzinama (velikim frekvencijama prijenosa) signal kod promjene logičkog stanja sa nule na jedinicu jednostavno ne stigne doseći svoj maksimum, pa možda ne bude prepoznat kao logička jedinica.

Koliki je prag prepoznavanja logičke jedinice i nule ovisi o karakteristikama same digitalne komponente koji koristimo. Načelno se mogu odabrati tri standardne brzine za I2C razmjenu podataka: 100 kHz, 400 kHz i 1 MHz. Za najnižu brzinu od 100 kHz dozvoljeno je vrijeme porasta od maksimalno 1 µs, a na našem oscilogramu vidimo da to vrijeme dostiže do 10 µs. Ovo se uvelike može poboljšati stavljanjem pull-up otpornika niže vrijednosti.

Takav je ugrađen u čip HS6760 pa idemo vidjeti kako izgleda signal na našem konkretnom primjeru.

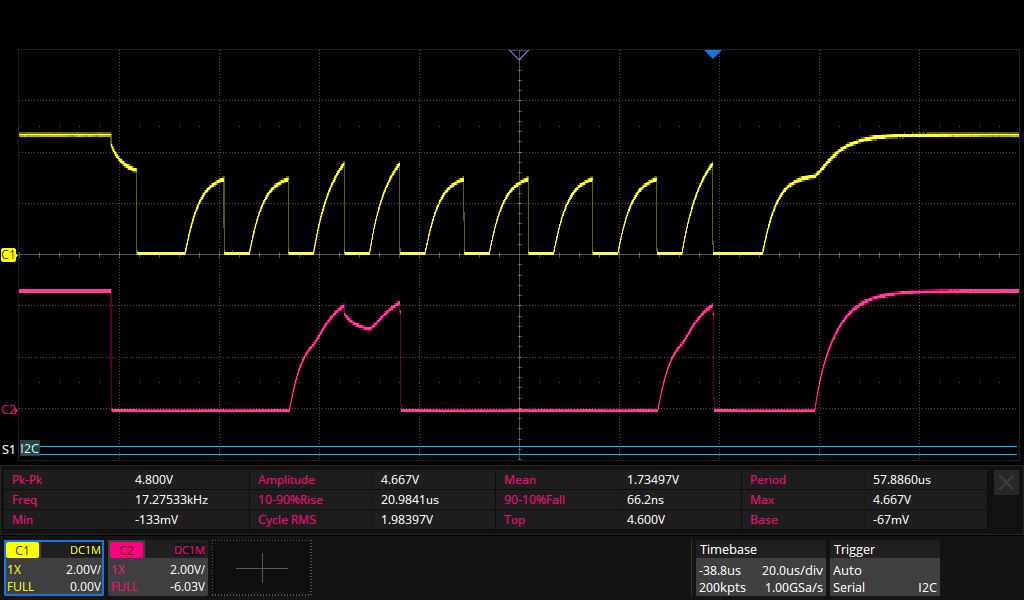

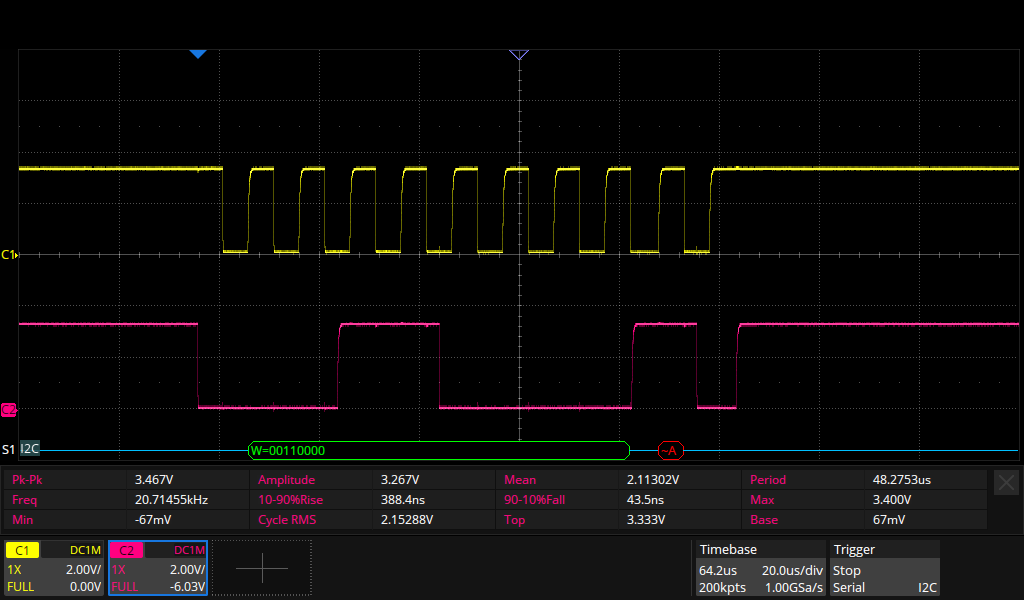

Ovdje vidimo I2C signal kada je čip HS6760 izravno spojen na Mega 2560, dakle samo sa internim pull-up otpornicima. Signal je loše stabilnosti i oblika te ga osciloskop ne može dekodirati.

Ovdje vidimo I2C signal kada je čip HS6760 izravno spojen na Mega 2560, dakle samo sa internim pull-up otpornicima. Signal je loše stabilnosti i oblika te ga osciloskop ne može dekodirati.

Kao što vidimo, za naš konkretni slučaj, čini se da interni otpornici od 40 kΩ u čipu HS6760 nisu dovoljni za dobivanje stabilnog signala brzog vremena porasta. Vidimo ovdje i neke dodatne smetnje u SDA signalu (crveno) kao i nepravilne amplitude SCL signala (žuto). Razlog ovome je što čip HS6760 napajamo preko regulatora 3,3 V na Mega 2560 ploči, a već smo rekli da su interni pull-up otpornici vezani na 5 V liniju.

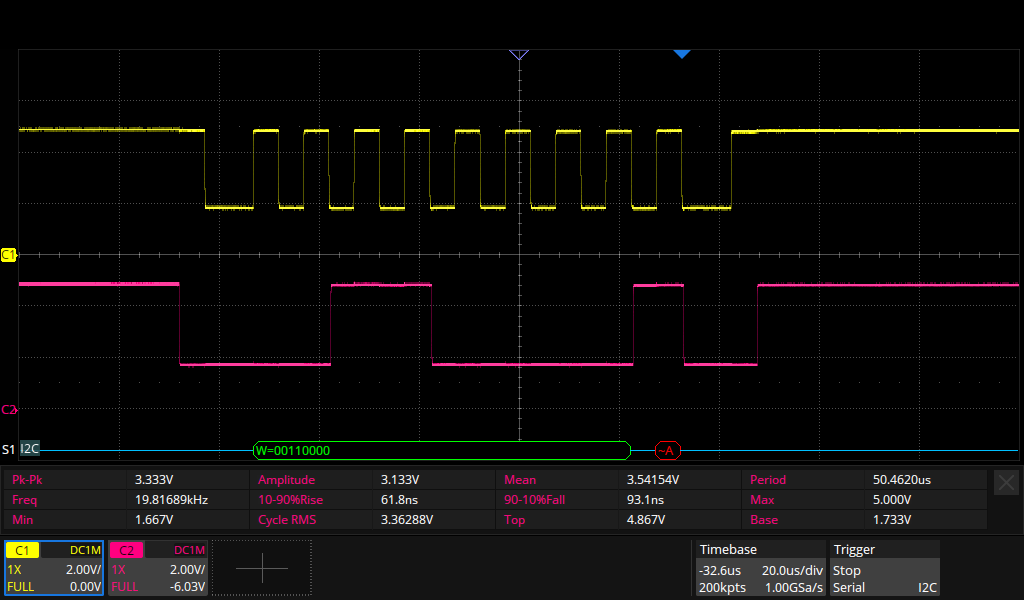

Ovo sam predvidio pa sam dodao pull-up otpornike od vrlo niskih 120 Ω. Ugradnjom tih otpornika signal ne samo što je dobio pravokutni signal, nego je on također ampitude 3,3 V.

Naime, ako se vrijednost pull-up otpornika smanji ispod neke razine (obično 1,5 kΩ), signal će istina biti više pravokutan ali tu će onda ujedno potrošnja struje (opterećenje) toliko porasti da će se amplituda signala početi smanjivati. Ne treba zaboraviti da se impuls u sustavu sa otvorenim kolektorom prenosi tako što se pozitivni pol napajanja (Vcc) zapravo kratko spaja na masu. Stoga neki „pull-up“ otpornik mora postojati jer ne možemo raditi baš čiste kratke spojeve između Vcc i GND. Ja sam u slučaju Mega 2560 smanjio pull-up otpornik na 120 Ω samo iz razloga jer sam time namjerno htio povećati opterećenje i smanjiti amplitudu signala sa 5 V na 3,3 V.

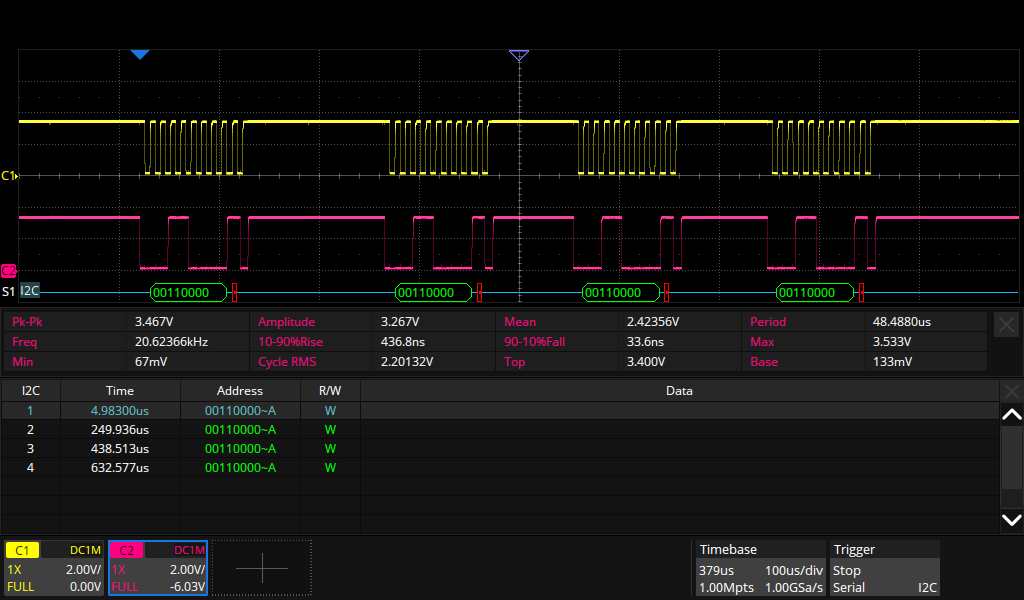

Pull-up otpornicima od 120 Ω sa Mega 2560 ploče se dobiva lijep pravokutni signal amplitude 3,3 V koji se ispravno dekodira.

Pull-up otpornicima od 120 Ω sa Mega 2560 ploče se dobiva lijep pravokutni signal amplitude 3,3 V koji se ispravno dekodira.

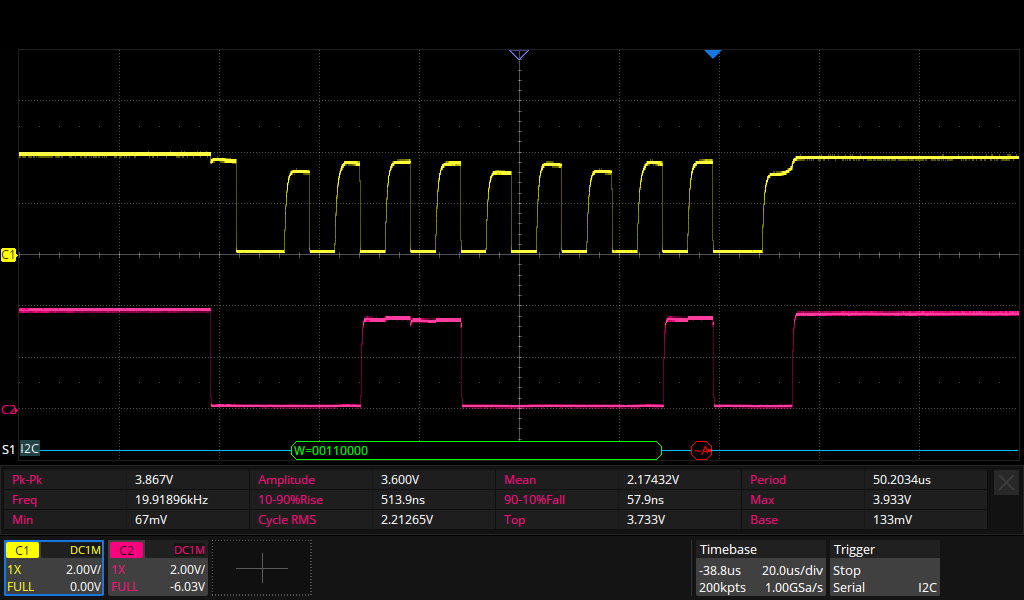

Međutim, kad se na tako „reguliran“ signal na Mega 2560 ploči poveže čip HS6760, naponi se ipak malo destabiliziraju. Do oscilacija i izobličenja napona dolazi jer sada I2C linije praktički paralelno napajamo sa dvije različite naponske linije koje su različito opterećene kod brzih promjena logičkih stanja.

No i unatoč tim nestabilnostima, signal se ipak može dekodirati na osciloskopu, a i desetke testova slanja i primanja podataka je uredno prolazilo.

Ovdje je isti slučaj kao i gore, samo što su sada na I2C linije dodani vanjski pull-up otpornici. Signal izgleda puno bolje i osciloskop ga bez problema dekodira, međutim, jasno je da to više nije posve čist i stabilan signal kao što je bio onaj bez spojenog čipa HS6760, posebice što se tiče amplitude.

Ovdje je isti slučaj kao i gore, samo što su sada na I2C linije dodani vanjski pull-up otpornici. Signal izgleda puno bolje i osciloskop ga bez problema dekodira, međutim, jasno je da to više nije posve čist i stabilan signal kao što je bio onaj bez spojenog čipa HS6760, posebice što se tiče amplitude.

Ono što smo primijetili na ovom testu i što puno više zabrinjava, to je što nakon slanja 7-bitne SLAVE adresu čipa HS6760 (0011000), od čipa ne dobivam pozitivni odgovor (A bit je Not-Acknowledge).

Sada bi svakako trebalo uložiti malo truda i napraviti stabilniju I2C komunikaciju, tako da male nestabilnosti isključimo kao mogući izvor problema.

Problemi sa naponskim razinama 3,3 V i 5 V

Činjenica je da je čip HS6760 predviđen za standard 3,3 V dok je Arduino Mega 2560 ploča dizajnirana za naponski standard 5 V. Probao sam razne kombinacije napajanja sa Arduino Mega 2560 pločom ne bi se naponi malo više stabilizirali: napajanje ploče preko USB porta, napajanje ploče preko DC konektora 7-12 V, napajanje čipa HS6760 preko 3,3 V regulatora na samoj ploči Mega 2560 i napajanje čipa preko zasebnog napajanja. Izgled I2C signala se nije bitno mijenjao.