Projekt ELEKTRONIČKA META

- Uvod

- Senzori

- Detektorska elektronika (diskretna)

- Detektorska elektronika (CPLD)

- Monitor

- Bežični link

Detektorska elektronika – CPLD

Već smo rekli da bi za našu metu sa 2×64 senzora trebalo 22 x SN74HC14 (Schmitt inverter), 32 x CD4044 (RS Latch) i 8 x CD74HC4067 (16-bitni multipleksori). Ako ne postignemo dovoljno otvaranje senzora trebat ćemo Schmitt invertere zamijeniti brzim komparatorima (32 x MCP 6564). Ovo je prilična količina čipova koje je treba što kompaktnije posložiti na tiskane pločice unutar okvira mete. Iako sam uspio nacrtati pločice koje bi to podržavale, sada ipak želim razmotriti jednostavnije alternative u vidu MCU, FPGA i CPLD.

MCU

Da bi 128 bita podataka obradili preko mikrokontrolera (programski) u tom kratkom vremenu, potreban nam je vrlo brz mikrokontroler (MCU) sa puno paralelnih ulaznih linija (najbolje neki 128 bitni MCU). Jeftine MCU razvojne pločice poput popularnog Arduina su prespore za taj zadatak (tipično 16 MHz) i premalog kapaciteta ulazno/izlaznih linija (I/O). Čak i sa najbržim (najskupljim) MCU platformama, poput Teensy 4.1 (600 – 816 MHz), Arduino Giga R1 (480 MHz) ili ESP32-P4 (400 MHz), te čak i uz dobru optimizaciju programskog koda, čitanje i obrada podataka sa svih 128 senzora teško bi se mogla obaviti za vrijeme brže od nekoliko mikrosekundi. To je za naš projekt presporo.

FPGA i CPLD

FPGA (Field-Programmable Gate Array) i CPLD (Complex Programmable Logic Device) su jednostavno rečeno „univerzalni“ logički čipovi koji omogućuju korisniku da ih sam programira na hardversku logiku koja mu je potrebna. To znači da jedan takav čip možemo konfigurirati da sadrži invertere, RS latcheve, multipleksore i sve druge logičke krugove koji su nam potrebni. Komparatore ne možemo konfigurirati jer to nisu digitalni nego analogni čipovi.

Pitanje je sada koju tehnologiju, FPGA ili CPLD, odabrati za naš projekt. FPGA nudi golem broj logičkih vrata, ugrađenu memoriju (RAM) i specijalizirane blokove za digitalnu obradu signala (DSP) te je primarno namijenjen za kompleksne zadatke poput obrade videa, umjetne inteligencije i mrežne infrastrukture. Nedostatak je što se arhitektura čipa temelji se na SRAM tehnologiji, što znači da je volatilan, odnosno gubi konfiguraciju čim nestane napajanja i mora je ponovno učitati iz vanjske memorije pri svakom pokretanju.

CPLD je jednostavniji čip koji se razvio iz rane programabilne logike (PAL/PLA) te se i koristi za kreiranje jednostavnijih logičkih krugova. Temelji se na Flash ili EEPROM memoriji, što ga čini nevolatilnim, odnosno zadržava program i nakon isključenja te je spreman za rad trenutno nakon paljenja. Zbog jednostavnijih internih veza, kašnjenje signala je fiksno i lako predvidljivo. Za naš konkretni projekt jasno je da je CPLD bolji, a također i jeftiniji izbor.

Nama treba CPLD koji podržava najmanje 128 I/O linija za senzore, te još desetak I/O linija za komunikaciju i eventualna proširenja. Također, umjesto čistog CPLD čipa, za samogradnju je puno bolja opcija odabrati neku CPLD razvojnu platformu koja već ima izvedene vanjske konektore, ugrađen regulator napona i oscilator i ostale popratne sklopove. Pretražio sam kinesku ponudu takvih CPLD platformi uspoređujući dva osnovna kriterija: broj dostupnih I/O linija i cijena samog CPLD-a.

EPM570 MAX II CPLD Development Module

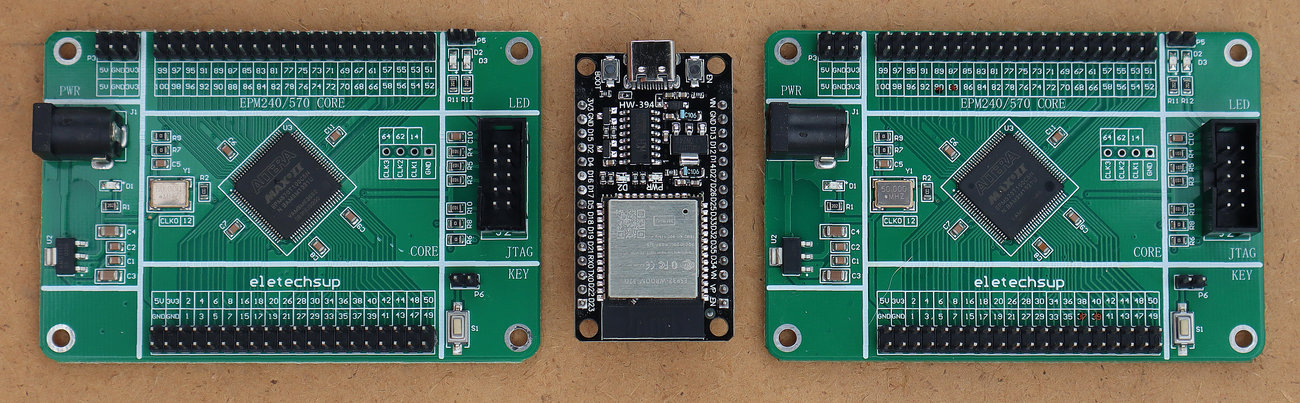

Konačni izbor je razvojna platforma sa CPLD čipom EPM570 (EPM570T100C5N) iz Intel/Altera MAX II serije. Na platformi su dostupna 72 I/O pina i ugrađen je takt oscilator na 50 MHz. Sama pločica je dimenzija 9×6 cm i košta oko 16 eura. Može se kupiti i 1 euro jeftinija inačica sa EPM240 čipom. Razlika između EPM240 i EPM570 je samo u logičkom kapacitetu (240 prema 570 logičkih elemenata) dok su po fizičkom obliku i većini funkcija gotovo identični. Prednost pločice sa EPM240 je što ima 4 I/O pina više, no to nama ne igra ulogu jer je za mrežu 2×32 senzora u oba slučaja dovoljna jedna pločica, dok za mrežu 2×64 senzora svakako moramo koristiti dvije takve pločice. Razlike u brzini su također zanemarive, kod EPM240 je kašnjenje 4,7 ns, a kod EPM570 je kašnjenje od 5,4 ns. Ovo su dakle vrlo brzi čipovi, 4 do 5 puta brži od najbržih diskretnih logičkih čipova.

Čitav hardver za senzorsku mrežu 2×64 senzora može se svesti na dvije CPLD pločice EPM570 i jednu ESP32 (ili Arduino) mikrokontrolersku pločicu. Za senzorsku mrežu 2×32 senzora dovoljna je jedna CPLD EPM570 pločica.

Čitav hardver za senzorsku mrežu 2×64 senzora može se svesti na dvije CPLD pločice EPM570 i jednu ESP32 (ili Arduino) mikrokontrolersku pločicu. Za senzorsku mrežu 2×32 senzora dovoljna je jedna CPLD EPM570 pločica.

CPLD EPM570

CPLD čip EPM570 dio je serije MAX II, koju je razvio Altera (danas dio Intela). Serija MAX II uvedena je sredinom 2004. godine te se kao većina CPLD čipova koristi za digitalno upravljanje, proširenje I/O portova, premošćivanje sabirnica (bus bridging), kontrolu sekvenci napajanja te u sustavima gdje je bitno da čip odmah proradi nakon uključenja (instant-on).

EPM570 sadrži 570 logičkih elemenata (LE) ili otprilike 440 ekvivalentnih makroćelija. Mi ćemo za naš projekt potrošiti manje od polovice tog kapaciteta. Međutim, ono što je nama važno to je dostupan broj korisničkih I/O pinova na razvojnoj pločici. S obzirom da imamo 128 senzora, potrebno nam je i najmanje toliko I/O pinova, plus desetak pinova za komunikaciju.

Jezgra EPM570 podržava do 160 I/O pinova, međutim, taj broj je dostižan samo u najvećem pakiranju (256-pin FBGA). Većina pristupačnih razvojnih pločica koristi 100-pinski TQFP paket (oznaka EPM570T100), koji fizički ima značajno manje izvoda. Tako sam i ja nabavio 100-pinsku TQFP razvojnu pločicu koja nudi maksimalno 72 korisnička I/O pina (pločica košta oko 15 eura).

Iako je ukupan broj pinova na kućištu 100, čak 28 pinova nije dostupno za opću namjenu (GPIO) jer su rezervirani za rad samog čipa: napajanje i masa, JTAG programsko sučelje, te drugi sistemski resursi na pločici. To znači da moramo koristiti dvije EPM570 pločice, no to nam i donekle odgovara jer će biti kraće ožičenje dvije osi senzora.

Na kraju ćemo iskoristiti apsolutno sve dostupne pinove na obje EPM570 pločice i bilo bi dobro da ih imamo još na raspolaganju, međutim, slične CPLD pločice sa više I/O pinova su već dosta skuplje i teže za nabavu.

Quartus Prime i Verilog

Quartus Prime (ranije poznat kao Quartus II) glavni je softverski alat za dizajniranje i programiranje Altera/Intel čipova. Omogućuje unos dizajna putem HDL jezika (VHDL, Verilog, SystemVerilog) ili grafičkih shema i nama prvenstveno služi za konfiguraciju pinova i prijenos gotovog dizajna na čip putem JTAG sučelja (vidi opis na stranici Projekt elektronička meta – Software).

Osim toga, Quartus Prime se može integrirati sa alatima poput ModelSim-a za funkcionalnu i vremensku simulaciju dizajna. Uključuje Timing Analyzer za provjeru hoće li dizajn raditi stabilno na zadanim frekvencijama. Sadrži alate poput Signal Tap logičkog analizatora koji omogućuje promatranje signala unutar čipa u stvarnom vremenu.

Iako je MAX II tehnologija stara više od dva desetljeća, Intel je službeno produžio podršku za MAX II seriju (uključujući EPM570) do 2035. godine. To znači da se čipovi i dalje proizvode uglavnom kao komponente za servis strojeva dizajniranih prije 15 godina. Za nove komercijalne projekte vjerojatno nitko više ne bira MAX II, radije se koristi moderniji MAX V ili moćniji MAX 10.

Novije verzije softvera Quartus (Quartus Prime Pro) više ne podržavaju stare čipove poput MAX II, tako da se za rad s EPM570 mora koristiti Quartus Prime Lite (besplatna verzija) ili Standard Edition, koji i dalje održavaju podršku za ove “legacy” uređaje.

Zašto sam odabrao MAX II umjesto nekog novijeg čipa?

Za ovo ima više razloga. Prvo, ja sam početnik u CPLD programiranju i lakše je razumjeti osnove digitalne logike na čipu s 570 elemenata nego se izgubiti u kompleksnosti MAX 10 čipa koji ih ima 50 000 (za moj projekt trebam oko 250 logičkih elemenata). Druga stvar je ona koju sam iskusio sa svim brzim modernim čipovima: nije problem kupiti jeftin i brzi čip, problem je u DIY uvjetima osigurati stabilnost rada takvog čipa. Stariji čipovi sa 180 nm tehnologijom su često puno tolerantniji na pogreške u spajanju nego moderni čipovi na 55 nm ili manje.

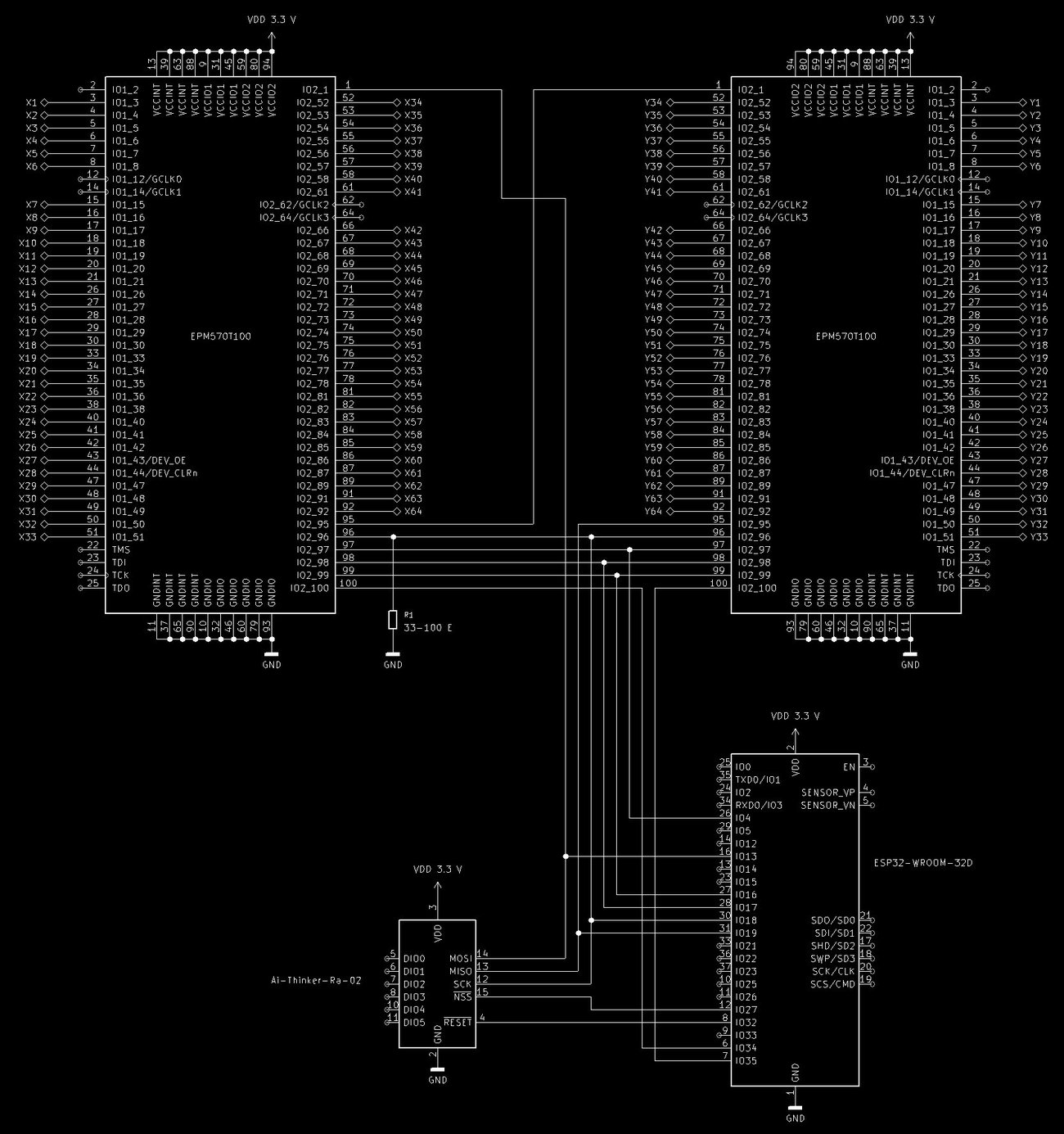

Elektronička shema prvog prototipa

Elektronička shema čitave elektronike na strani mete sada se sastoji od četiri jeftina, lako nabavljiva modula. Čitav sistem uključujući i senzore radi na 3,3 V.